# **Advanced Architecture**

Computer Science Honours Rhodes University – 2012

Philip Machanick

This material may be freely reused provide the source is acknowledged.

Copyright © Philip Machanick 2012

# **Contents**

| Li | st of 1 | Figures       |                                         | v   |

|----|---------|---------------|-----------------------------------------|-----|

| Li | st of ' | <b>Fables</b> |                                         | vii |

| 1  | Intr    | oductio       | on.                                     | 1   |

|    | 1.1     | Measu         | rement                                  | 2   |

|    | 1.2     | Design        | n Approaches                            | 3   |

|    | 1.3     | Perfor        | mance Factors                           | 4   |

|    | 1.4     | Archit        | tecture Areas                           | 5   |

|    |         | 1.4.1         | Memory Hierarchy                        | 6   |

|    |         | 1.4.2         | Hardware Layers                         | 6   |

|    |         | 1.4.3         | Hardware-Software Layers                | 7   |

|    |         | 1.4.4         | Hardware-Software Interaction           | 8   |

|    |         | 1.4.5         | Instruction Set Design                  | 9   |

|    |         |               | Styles of Instruction Set               | 9   |

|    |         |               | Design for Performance                  | 11  |

|    |         | 1.4.6         | Input and Output                        | 12  |

|    |         | 1.4.7         | Parallelism                             | 12  |

|    |         |               | Instruction-Level Parallelism           | 13  |

|    |         |               | Multiprocessor and Multicore            | 13  |

|    |         |               | GPUs                                    | 14  |

|    |         |               | Warehouse-Scale Computing and the Cloud | 15  |

|    | 1.5     | The O         | ther Edge                               | 16  |

|    | 1.6     | Structi       | ure                                     | 17  |

| 2  | Men     | nory an       | nd Quantitative Design                  | 18  |

|    | 2.1     | Memo          | ory Systems                             | 18  |

|    |         | 2.1.1         | Organization Principles                 | 18  |

|    |         | 2.1.2         | Levels of the Hierarchy                 | 20  |

|    |         |               | Registers                               | 20  |

| CONTENTS | iii |

|----------|-----|

|----------|-----|

|   |      | TLB                                                           | 21        |

|---|------|---------------------------------------------------------------|-----------|

|   |      | Caches                                                        | 22        |

|   |      | Main Memory                                                   | 25        |

|   |      | Paging Device                                                 | 27        |

|   | 2.2  | Measurement                                                   | 28        |

|   | 2.2  | 2.2.1 Architecture-Oriented Measures                          | 28        |

|   |      | 2.2.2 Benchmarking                                            | 29        |

|   | 2.3  | Putting it All Together: Measuring Memory Systems Performance | 30        |

|   |      | 2.3.1 Back of the Envelope Calculation                        | 31        |

|   |      | 2.3.2 Profiling                                               | 35        |

|   |      | 2.3.3 Trace-Driven Simulation                                 | 35        |

|   |      | 2.3.4 Whole-System Simulation                                 | 36        |

|   |      | 2.3.5 More Detailed Approaches                                | 36        |

|   |      | 2.3.6 Summary                                                 | 37        |

|   |      | •                                                             |           |

| 3 | Pipe | elines and ILP                                                | 39        |

|   | 3.1  | Simple Pipelines                                              | 40        |

|   |      | 3.1.1 Pipeline Limitations                                    | 42        |

|   |      | 3.1.2 Pipeline Performance                                    | 42        |

|   |      | Case Study                                                    | 43        |

|   |      | Hazards                                                       | 44        |

|   | 3.2  | More Exotic Pipelines                                         | 53        |

|   |      | Static scheduling                                             | 55        |

|   |      | Dynamic scheduling and better branch prediction               | 58        |

|   |      | Compiler-Exposed ILP                                          | 61        |

|   | 3.3  | Summary                                                       | 62        |

| 4 | Mul  | tiprocessors                                                  | 64        |

| • | 4.1  | Multiprocessor Models                                         | 64        |

|   | 4.2  |                                                               | 66        |

|   | 4.3  | Shared Memory Principles                                      | 70        |

|   | 4.5  | False Sharing                                                 | 71        |

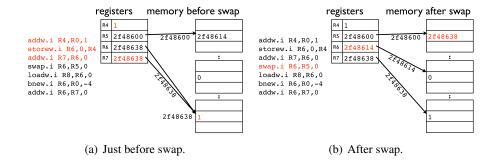

|   |      | Locks                                                         | 73        |

|   | 4.4  | Summary                                                       | 76        |

|   | 7.7  | Summary                                                       | 70        |

| 5 | GPU  | Js                                                            | <b>78</b> |

|   | 5.1  | Vector Processing                                             | 79        |

|   | 5.2  | SIMD Extensions to Instruction Sets                           | 83        |

|   | 5.3  | GPUs                                                          | 84        |

|   | 5.4  | Review                                                        | 87        |

| iv | CONTENTS |

|----|----------|

| 6  | War    | rehouse-Scale Computing           | 90  |

|----|--------|-----------------------------------|-----|

|    | 6.1    | Fault tolerance and dependability | 91  |

|    | 6.2    | Programming model                 | 93  |

|    | 6.3    | Hardware Design                   | 96  |

|    | 6.4    | Warehouse Design                  | 99  |

|    | 6.5    | Historical Perspective            | 99  |

| 7  | Pred   | licting Breakthroughs             | 104 |

|    | 7.1    | Predicting the Past is Easy       | 105 |

|    | 7.2    | Limits to Trends                  | 105 |

|    | 7.3    | Really New Stuff                  | 107 |

| Re | eferen | ices                              | 109 |

| A  | Min    | imal Instruction Set              | 124 |

# **List of Figures**

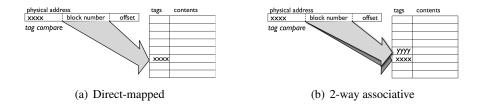

| 2.1  | Cache addressing                               |

|------|------------------------------------------------|

| 2.2  | Example of miss rate calculation               |

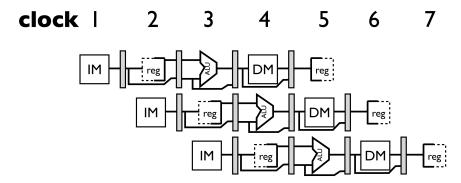

| 3.1  | Progress through a 5-stage pipeline            |

| 3.2  | Pipeline progress with datapaths               |

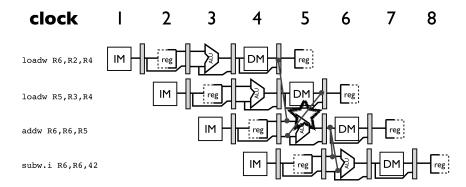

| 3.3  | Our code without pipeline bubbles              |

| 3.4  | Our code with stalls                           |

| 3.5  | Approaches to reducing stalls                  |

| 3.6  | Limits of forwarding                           |

| 3.7  | Branch-induced stalls                          |

| 3.8  | Two-bit branch predictor state transitions     |

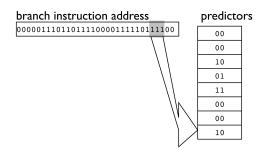

| 3.9  | Finding a branch prediction                    |

| 3.10 | Dependences in one iteration of the loop       |

| 3.11 | Simple two-instruction dispatch schedule       |

| 3.12 | Dependences in two instances of the loop       |

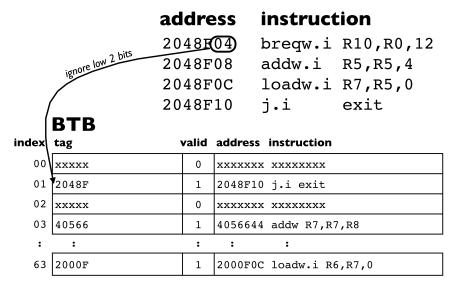

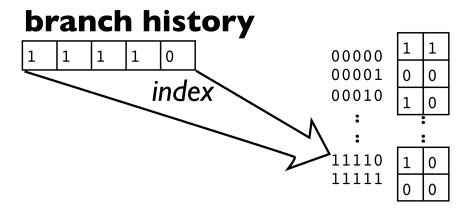

| 3.13 | Possible branch table buffer organization      |

| 3.14 | Two-level predictive branch 61                 |

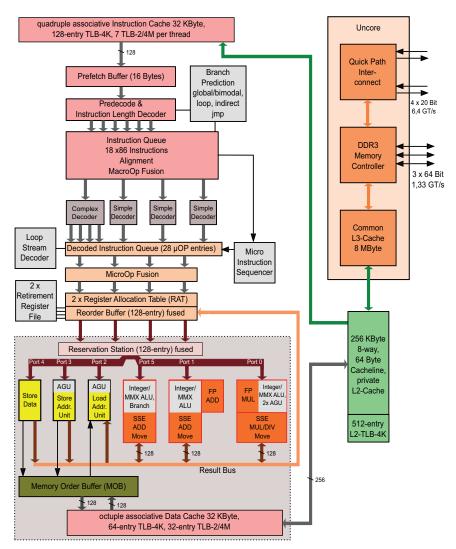

| 4.1  | The Intel Nehalem architecture                 |

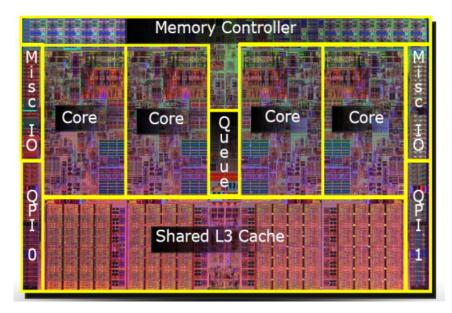

| 4.2  | The Intel Nehalem die showing major components |

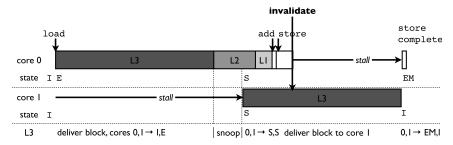

| 4.3  | False sharing example                          |

| 4.4  | Simple ticket lock                             |

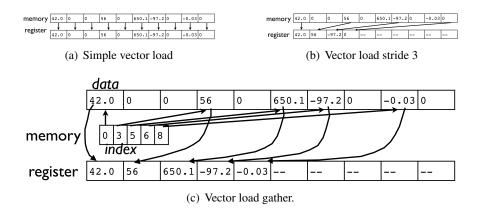

| 5.1  | Variations on vector loads                     |

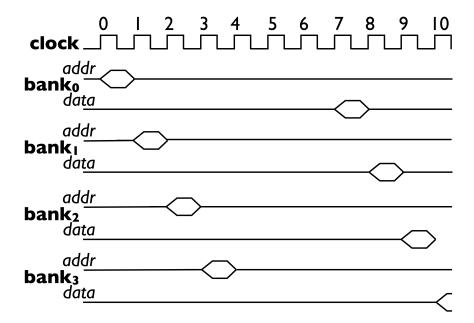

| 5.2  | The principle of multiple memory banks         |

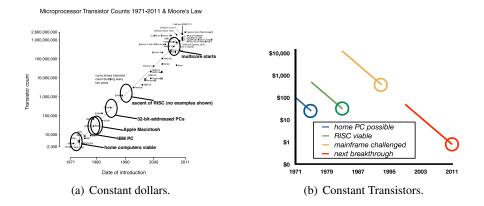

| 7.1  | Two views of Moore's Law                       |

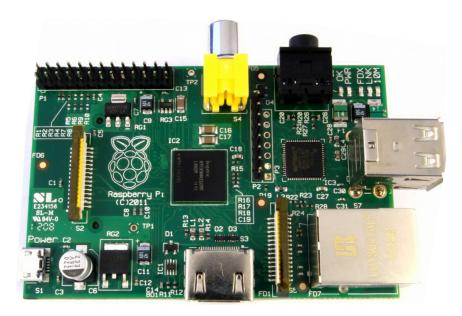

| 7.2  | Raspberry Pi                                   |

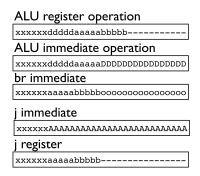

| A.1  | Minimal RISC instruction set                   |

| Δ 2  | Possible instruction encoding 126              |

| vi |     |                              |  |  |  |  | Ll | ST | O | FF | IG | IJ | RES |

|----|-----|------------------------------|--|--|--|--|----|----|---|----|----|----|-----|

|    | A.3 | Refined instruction encoding |  |  |  |  |    |    |   |    |    |    | 128 |

# **List of Tables**

| 2.1 | Common terminology                              | 19 |

|-----|-------------------------------------------------|----|

| 2.2 | Performance parameters                          | 31 |

| 2.3 | Performance improvement measures                | 31 |

| 3.1 | Simple instruction set for examples             | 46 |

| 4.1 | Intel Nehalem latencies                         | 72 |

| 6.1 | Dependability terminology                       | 92 |

| 6.2 | Dependability example                           | 92 |

| 6.3 | Expected number of failures for 2,500 computers | 92 |

| 6.4 | Performance parameters for scalability          | 96 |

# 1 Introduction

**♦** OMPUTER ARCHICTURE is a rapidly moving field yet a few things have held good over the last three decades. Before the RISC movement of the late 1970s, much computer architecture was based on gut feel, or poor communication between the hardware and software sides of design teams. For example, the hardware people may decide that setting up the call stack involves tedious repetition and to be nice to the compiler people, they roll this all into one instruction. Only, because they didn't consult the compiler people, the instruction they design isn't useful and is never used. Then when they try to implement a more aggressive version of the design, they find all the complicated instructions they weren't asked to design by the software people make it hard to produce a more aggressive design. Related to this communication issue is a lack of standards for quantifying improvements. In the 1970s, Gene Amdahl, a former IBM engineer who split with IBM to form his own high performance computing company, formulated a speedup limitation [Amdahl 1967] that became known as Amdahl's Law. In essence this says that to calculate the effect of a speed improvement, you need to take into account the entire run time including parts that are not sped up. An apparently obvious revelation, it's a point often forgotten when extolling some brilliant enhancement (not only to computer systems).

What created an impetus for improved standards in quantifying performance was a dispute that arose between two schools of computer architecture, the high-level-language oriented approach, and the simplicity-oriented approach. The latter gained credibility as early as the 1960s, when Seymour Cray, at that time working for a relatively small company called Control Data, produced a design that was much faster than the best the market leader IBM could produce. However, many designers still argued that a machine instruction set closer to high level languages was more efficient because even though each instruction may be slower than with a design closer to the hardware, you needed fewer instructions. This argument carried some weight when memories were relatively small, and hardware complexity could be replaced by *microcode*, a very low-level instruction set that interpreted the actual machine instructions. Microcode was stored in a ROM that

was many times faster than DRAM, so frequent accesses of *microstore* as the cost of fewer instruction fetches was a reasonable trade-off. However, as DRAM speeds caught up with ROM speeds and it became viable to implement caches in fast SRAM, the case was less clear. It took a landmark paper in 1980 [Patterson and Ditzel 1980] to fire up a new movement inspired by Seymour Cray's 1960s designs [Thornton 1963] to push the case for simpler instruction sets, and that push led to a more quantitative approach to architecture design and evaluation. In particular, to win the case for simplified instruction sets, the RISC (reduced instruction set computer) movement began a move to more scientific principles in measuring alternative designs, with an emphasis on *repeatable* experiments that were representative of *real workloads*.

In this course we learn about tools and techniques for measuring performance, how architectures are designed and what factors are useful to consider when comparing performance of alternative designs. We related these issues to a range of different areas of architecture design: memory hierarchy, instruction set design, input and output, and parallelism in various forms.

# 1.1 Measurement

Computer architecture measurement falls into two broad categories: evaluating existing designs and implementations, and evaluating design alternatives. In the first category, we can run standard benchmarks (software that represents a workload of interest) and we can also use simulations so as to produce repeatable run times. In the second category, we mainly rely on simulations because it is too expensive (even using reconfigurable hardware, such as FPGAs) to create multiple real variations in a design to check the effect of changes in design parameters.

Whichever approach we use, we try to adhere to a few essential principles of the scientific method:

- repeatable running the same experiment twice should give the same result and we should report enough detail so others can redo the experiment

- *separation of variables* where more than one factor can influence performance in a way that cannot be separated out, only vary one such variable at a time

- representativity the experiment should represent something real to those interested in the evaluation, not an artificial exercise that will not rank alternative designs the same way as would real usage

While these principles seem obvious, the quantitative approach was novel enough at the time that two senior academics, David Patterson at the University of California, Berkeley and John Hennessy at Stanford, felt the need to codify the principles in an academic text in 1990 [Hennessy and Patterson 1990] that has subsequently entered its fifth edition [Hennessy and Patterson 2012], and these principles are now routinely observed in mainstream computer architecture research, which was not the case when I first became interested in the field in 1980.

The fact that we now have well-established scientific principles of architecture measurement doesn't mean that the field is devoid of creativity or innovation. However, that innovation now has to be based on reasonably sound principles. Even so, some large mistakes are still possible, for example, the attempt by Intel to break out of their IA32 architecture with the IA64 (Itanium) design, which failed to achieve its performance goals or wide market acceptance.

A scientifically sound basis for measurement only allows us to be accurate about making comparisons: it does not remove the requirement of thinking up innovations, because someone has to derive the new ideas to compare with old.

# 1.2 Design Approaches

Given all that, how do we arrive at innovations?

Much of the early computer architecture work up to the 1970s set the scene for widely accepted design alternatives today. A fair fraction of innovation today involves rediscovering old ideas that worked well in a different form factor, and finding that technology today makes those ideas work well once more. Much of Seymour Cray's work in the 1960s was in essence reinvented by RISC designers in the 1970s through to around 2000, as it progressively became possible to fit more of the features of his multichip designs onto a single-chip CPU. Remarkably, very little in modern designs wasn't found in his landmark CDC 6600 of 1962, including hardware to support multiple instructions per clock cycle and out of order execution.

Today, a good starting point for looking our for potential for innovation is to examine various trend lines and work out when new design trade-offs become possible. Possibly the most famous of these trends is *Moore's Law*, an observation that the number of transistors at a given price doubles about every 2 years [Moore 1965]. There are others, like the quartering of the cost of DRAM every 3 years, and the much slower speed improvement of DRAM. Understanding how long these trends can persist and when a change in technology is predictable opens up opportunities for architecture research. For example, in the 1990s, I observed that the speed gap between DRAM and CPUs was heading for similar numbers as measured by lost instruction execution opportunity to the speed gap between CPUs and paging devices when virtual memory was first invented. That led to the *RAMpage* project, of which I cite a fraction of the research outputs

here [Machanick et al. 1998; Machanick 2000; Machanick and Salverda 1998; Machanick 2004].

In another breakthrough, which led to a major change in the whole industry, a Nigerian academic at Stanford University Kunle Olukotun [Olukotun et al. 1996] made a case for replacing very aggressive single-core designs by what are now known as multicore designs. In essence his argument (backed up by design studies and simulations) is that the potential for speedup of a single core design is limited by how much instruction-level parallelism is available, whereas a multicore design can gain speed from several dimensions. A clever compiler can convert instruction-level parallelism into threads, code already designed to run threads or multiple processes can speed up, and multiprogramming workloads (as on a typical operating system where there may be dozens of processes, many not visible to the non-technical user) can also see a speed gain. Multicore designs have in recent years also gained in utility because they create more options for scaling both performance and energy use.

Yet another approach to looking for breakthroughs in architecture is studying roadmaps of predicted future technology<sup>1</sup>. In one example, Trever Mudge at the University of Michigan picked up the likelihood that vertical stacking of dies (a die is a chip without the packaging) was on the horizon, and he explored the implications of this technology for making a package tightly integrating DRAM and a multicore CPU design. The resulting design has a number of advantages. Because through-chip *vias* (conductors) can be as fast as within-chip communications and wide buses are practical to construct in this form, the CPU-DRAM speed gap can be considerably reduced. Since the CPU wastes less time waiting for DRAM, a given level of performance can be achieved with a slower clock, reducing he problem of heat dissipation out of a compact package. The resulting PicoServer design [Kgil et al. 2006] and its successor Centip3De [Fick et al. 2012] may at some stage emerge as a commercial product; even if it does not, it is a good illustration of looking out for technologies that may later become viable.

# 1.3 Performance Factors

When considering performance, we need to take into account several axes. Depending on the target appllication or market, different axes may be more important. The most significant ones are

<sup>&</sup>lt;sup>1</sup>International Technology Roadmap for Semiconductors http://www.itrs.net/ is a good example.

Architecture Areas 5

• *cost* – not only of one component such as the CPU, but overall packaging and environment costs

- speed again, not only one component contributes to speed (remember Amdahl?)

- *energy* in some applications like mobile computing, energy is a first-class concern but even in large-scale computing, energy is a limiting factor

- scalability a design that works at many scales means early expensive versions can be sold into high-margin markets like high-end servers, while older designs can be sold into high-volume markets to maximise amortisation of costs

- longevity one of the most classic errors of hardware designers is to fail

to take into account the rate at which technology improves: too small

an address space is one of the most common reasons once-successful

architectures have had to be abandoned

Cutting across these axes are two approaches to performance that can be in conflict:

- latency time to complete a specific operation or service

- throughput average rate of work completion

Low latency is what the user desires; high throughput is what the accountants want. Low latency means you have a responsive system, but that responsiveness can be bought at the expense of lowering throughput, by ensuring that the system is not busy when you want a response.

In this course I examine case studies of performance covering as many of these axes as is practical, depending on the nature of student projects.

# 1.4 Architecture Areas

Computer architecture is broadly speaking design principles of any area of the computer system including the hardware and any area where hardware and software interface. It's convenient to divide architecture down into different areas, though these necessarily interact. For example, the memory hierarchy includes components that use the IO system, and efficient implementation of IO requires design with the memory hierarchy in mind. So as we divide the architecture world for clarity, remember that the division is not absolute.

# 1.4.1 Memory Hierarchy

The need for a memory hierarchy arises from the fact that memory components fast enough to keep up with the CPU are many times more expensive than slower memories. Fortunately, the *principle of locality* says that you a program uses a relatively small part of its address space at a time. Locality is generally divided into two types:

- *temporal locality* a memory location that is referenced is likely to be referenced again soon

- *spatial* a memory location near a location that is referenced is likely to be referenced soon

The definitions of "soon" and "near" depend on how big the speed gap is between layers. If the speed gap is big, we stretch the definitions out to longer in time and space, because we can less afford the penalty of accessing slower memory.

In an operating systems course, we focus on locality as it applies to virtual memory; here we also consider hardware layers of the memory system, including caches, the TLB (translation lookaside buffer: a small cache of recent page translations) and registers.

# 1.4.2 Hardware Layers

It is useful to divide computer hardware into logical layers. As seen by the user (or, in today's world, the compiler and related tools like the linker), there is the machine code layer. This layer cannot change much in basic functionality without losing the user base. If you have to recompile or relink your code to run on a new generation of a particular vendor's design, that takes away a reason to stay loyal to that vendor. The *instruction set architecture* or *ISA* is such an important part of a designs identity and its ability to retain a user base that the ISA is often referred to as the architecture (the IA32 architecture, the PowerPC architecture, etc.).

The ISA is not only characterised by a set of instructions but also by the available machine registers, the memory bus size and instruction modes such as supervisor and user mode that implement protection. The idea of an ISA essentially developed with the IBM 360 series of the 1960s [Amdahl et al. 1964], which was the first to feature a whole family of designs launched at once that could run the same programs, subject only to resource limits not differences in the type of code that could execute.

The ISA can be implemented many different ways and remains the same ISA as long as the same programs can run (give or take constraints like memory size and available peripherals).

Architecture Areas 7

Some details that can vary include the pipeline, extra copies of the registers to support implementation details like hardware multithreading support and out of order execution, branch prediction and variations in the memory hierarchy. All these variations are below the level of the ISA because they are hidden (other than performance impacts) from anything assuming the ISA as a given.

One area that is not obvious to the user (even a compiler writer) that is hard to change in practice is hardware support for VM. If this changes, unless the old approach is maintained for backward compatibility, every operating system using the new design will need to be modified, since hardware support for VM is tightly integrated into the software side of VM implementation.

# 1.4.3 Hardware-Software Layers

The operating system provides a layer of abstraction that hides the bare metal from the user, and some parts of the system architecture may involve hardware and software components. The most obvious of these is the virtual memory system that cannot be implemented effectively without hardware support (otherwise, every memory reference would take several times as long as without VM, since it must be looked up and translated, as well as checked for validity).

There are other aspects of the system where hardware and software play a role. In some earlier microprocesor designs including some RISC designs and some implementations of the Intel IA32, significant speed gains could be had from reordering instructions. Such reordering required recompilation in most cases, and was seldom done for the very good reason that the next generation had a different optimal ordering of instructions.

In yet another area, IO involves hardware-software cooperation. IO is very slow compared with the CPU and RAM and that speed gap has to be hidden. An operating system typically schedules IO-bound processes with higher priority than CPU-bound processes for two reasons. If CPU-bound processes run to completion while there are still IO-bound processes in the system, there is no work to be done while waiting for IO. Secondly, if IO-bound processes are able to use the CPU, it's best to give them more time than CPU-bound processes so they can make progress. An operating system has a range of strategies to hide the latency of IO in addition to scheduling policy. Here is a quick summary:

- scheduling IO-bound processes have higher priority than CPU-bound processes

- buffering slightly different effects for input and output:

- input read more than absolutely needed, relying on spatial locality not to waste the extra IO because it's usually more efficient to transfer

in large blocks

- output don't wait for writes to complete: dump output to memory and let the device empty the buffer in its own time

- cacheing keep data (or code) in a faster layer of memory as long as

possible; buffering can be a form of cacheing if the contents are available

for repeated use

- *spooling* for devices that have to accept a job to completion, spooling is a specialist kind of buffering that stores the data until it's that job's turn (most often used for printing)

- specialist IO hardware in some systems IO is hived off to a separate specialist CPU relieving the main CPU of the detail of IO

These represent some of the strategies used by an operating system; we do not cover much detail here since an OS course has more space to do so.

# 1.4.4 Hardware-Software Interaction

Given overlaps in hardware and software, how important is it for software to be aware of hardware, and vice-versa? In addition to the issues raised above of communication between parts of the design team, users of a design can benefit from knowing how their software interacts with hardware.

Some areas where this knowledge can apply include:

- *memory-sensitive algorithms design* understanding of how the cache and VM subsystems work can have a large effect on performance [Lam et al. 1991; Machanick 1996; Xiao et al. 2000; Rahman and Raman 2000]

- balancing VM use and IO in an experiment, I ran quicksort on randomly generated data varying the size until I ran out of RAM and paging occurred. I rewrote the code so it sorted a section at a time, storing most of the data on disk, using mergesort to merge only as much as would fit into RAM at one time. This ran a lot faster than relying on VM. No big surprise. But what was a bit surprising was that it was not significantly slower than quicksort on data that did fit into RAM.

- efficient use of shared memory with multithreaded code or processes with shared memory, a clear understanding of cacheing makes a big difference to performance [Machanick 1996]

- role of VM hardware support understanding how VM is supported in hardware can also make a big difference to performance [Machanick 1996]

Architecture Areas 9

In this course we explore some of the issues; since the 1990s when multiprocessor systems were relatively expensive, some hardware-software interaction concerns have found their way to the mass market because of the proliferation of multicore designs.

# 1.4.5 Instruction Set Design

Instruction set design used to be a core area of computer architecture. It is less so now that it's clear that RISC is fundamentally a good idea, but the Intel IA32 architecture isn't going to go away despite this.

# **Styles of Instruction Set**

Prior to the RISC (reduced instruction set computer) movement, there were two major schools of design:

- ad hoc do something that feels right and hope for the best, making a few trade-offs like make common instructions shorter than less common ones to reduce memory footprint at the expense of making instruction fetch and decoding harder

- *high-level language oriented* or *HLL* design the instruction set to be easier for compiler writers to generate code

In the first category, we have some of the most enduring designs. The Intel IA32 developed out of a processor with a 16-bit address space, the Intel 8086, which was upgraded to a 32-bit address space with the 80386 in 1985 and now includes 64-bit implementations. The IA32 has endured because it was adopted for IBM's PC design, which developed a massive market, and also because Intel was able not only to throw massive resources at improving its performance against the odds, but had very skilled engineers working around the inherent flaws in the design. The IBM 360 architecture [Amdahl et al. 1964; Gifford and Spector 1987] is another that endured for decades despite clear flaws (in terms of subsequent knowledge on how to design for performance). The 360 endured because IBM was one of the first computer companies to sell on service rather than technology, and because the design had a few key things right: it was designed for 32-bit addressing ahead of much of the competition, and had an adequate number of registers, a critical feature for achieving high performance. IBM, like Intel, had very skilled engineers able to work around inherent flaws in the design.

In the second category, one of the more successful examples is the Burroughs B5000 architecture [Mayer 1982], which used a stack-based instruction set and had hardware support for arrays including bounds checking (a hardware data

structure called a *descriptor* stored details of each dimension of the array). Memory was tagged with extra bits representing the type of contents of a machine word, further supporting error checking. Since the hardware could determine the type from the tag bits, there was only one instruction for each basic operation like addition (not a separate instruction for floating point, integer and various precision alternatives). The instruction set was very compact, since stack instructions do not need register names let alone memory addresses except to move data onto or off the stack, and in an exception to common practice, the hardware and software teams worked in close collaboration. Unusually for its time, the system software was written in a high-level language (a version of Algol 60, a language with some following in academia), and the operating system was distributed as source code. The Burroughs machines were not particularly fast if you measured the run of a single program but had a very efficient VM system, and easily outperformed machines that were a lot faster on paper, with real workloads. Unfortunately, Burroughs designed their array support assuming the Algol 60 approach of storing multidimensional arrays in row major order, whereas the scientific community mostly chose to use FORTRAN, which requires arrays to be stored in column major order, causing significant complications in generating efficient FORTRAN code.

The Burroughs example illustrates one of the hazards of HLL-oriented design: high-level languages differ enough that it's hard to do a design that's good for one without serious compromises for implementing other languages.

One of the less successful examples of HLL designs is the Intel 432 [Organick 1983]. The 432 had very fine-grained protection, supposedly to support object-oriented coding, but had very poor performance [Colwell et al. 1988], and didn't ever gain significant market share.

The IA432 illustrates another hazard of HLL-oriented design: it can result in poor performance, especially when insufficient attention is paid to any of practicalities of hardware implementation and usability of features in compilers.

More recently, hardware support for executing Java bytecode has emerged. However, just in time (JIT) compilers reduce the advantage of a Java machine. One implementation of partial hardware support for Java targets small devices with real-time requirements [Schoeberl 2008]. Some niches may justify specialist designs though on the whole it's easier to use a language that's a better fit to the problem than to design hardware to work around limitations of a language (e.g., garbage collection makes for unpredictable execution times, a problem for real time).

By contrast, the RISC movement specifies a very simple regular approach to instruction set design:

• fixed instruction length – all instructions are the same length, making it easy to fetch and decode multiple instructions in parallel

Architecture Areas 11

• *load-store architecture* – all memory references are loads (copy to register) or stores (copy from register); arithmetic and logic unit (ALU) operations are always on registers

- *standard operands* ALU operations always operate on 1 or 2 source registers and one destination register

- bounded execution time with the exception of excursions down the memory hierarchy, instructions have clearly defined execution time

- *simple control* the number and type of branch instructions is limited (usually unconditional jump, and a few conditional branches)

- *large general-purpose register file* a small number of registers, registers with specific purposes or setting logic conditions in condition codes makes it harder for compiler writers to generate code, and harder for hardware to reorder instructions

Some RISC designs compromise on details, e.g., a number do use condition codes. Nonetheless RISC architectures are generally very similar, unlike other classes of ISA design that differ widely.

We see next why the RISC movement claims advantages over the other approaches. At this point, note that even with the Burroughs design where the hardware and software teams did work in close collaboration, the fact that their pesky customers chose to use a different language for programming meant that much of their good work was wasted.

## **Design for Performance**

The RISC movement is based on a few key observations of how performance is achieved. First, to make the overall system fast, you need to have the highest possible clock speed and rate of instruction flow through the system. The latter works best if you can implement an efficient pipeline. A pipeline is inherently inefficient if the stages are not all the same length (the longer stages will force the shorter ones to idle). To implement a fast clock speed, relatively short pipeline stages help. If there are many variations in type and size of instruction, these things become harder to achieve.

Second, an important principle is *make the common case fast*. This seems contrary to the lesson of Amdahl's Law that the best speed gains arise from making everything faster. However if you calculate speed improvement based on accurate performance measurement, you can quantify this effect. For example, having to run 50% more instructions as the price for doubling clock speed is probably a

win (though you need a comprehensive measurement that takes into account other effects like changes in memory hierarchy use). By contrast, introducing a few special-case instructions that are rarely used but make it hard to scale up the clock speed is seldom a win. Again, quantifying makes the case, not gut feel or hand waving.

To take an example, RISC architectures generally implement a call with several (general-purpose) instructions, rather than using a special instruction to set up a stack frame and store the return address. While this increases the instruction count, the absence of special instructions makes it easier to implement an aggressive pipeline. At the cost of of occasionally using more instructions, the overall system is faster. We can quantify this effect if we know how much faster the clock speed can be made, or how the pipeline can be improved in other ways by simplifying the instruction set design, and calculate the net gain. The need to do this sort of calculation to convince RISC sceptics was the start of the modern approach to quantitative design.

## 1.4.6 Input and Output

IO is an important part of systems design because most IO devices are so much slower than the rest of the system. A disk for example may take of the order of 10ms to do a seek (move the head to the right track). DRAM access is almost a million times faster, and a 2GHz CPU if executing only one instruction per clock takes 0.5ns per instruction peak is 20-million times faster. If you have an aggressive pipeline executing several instructions per clock the speed gap is even greater (before you consider keeping up with multiple cores).

In this course we do not study IO in detail; many of the performance issues are better dealt with in an operating systems course. At the hardware level we can consider various modes of interfacing, the relationship between latency and throughput (or bandwidth in the IO context) and trends in device technology.

# 1.4.7 Parallelism

Every now and then when progress in a given approach to technology appears to be heading for a dead end, parallelism appears as the solution. What usually happens is a new approach to sequential programming appears, and all the complexities of parallel programming lose their attraction. Over time many models of parallelism have appeared, and some have proved enduring, while others keep resurfacing as packaging trade-offs change, and the reason they were abandoned is forgotten.

As long as Moore's Law was effectively delivering double the performance every 2 years or so, there was little benefit in writing parallel code for performance unless you could afford a large-scale system. Any system that achieved a speedup

Architecture Areas 13

over a serial implementation (measured as  $time_{serial}/time_{parallel}$ ) of less than 4 would be overtaken by faster hardware in a year or two, sometimes sooner than the time it took to achieve an efficient parallelisation.

#### **Instruction-Level Parallelism**

Before the multicore era, the most common form of parallelism was instruction-level parallelism (ILP), because it took no effort from the programmer. Provided the hardware can find more than one instruction ready to run at the same time, ILP provides speedup at the expense of hardware complexity, a trade-off increasingly justifiable as the number of transistors per chip at a given price point increases.

ILP however has some inherent limits. There's a limit to how much inherent parallelism that exists at instruction level because of dependencies between instructions [Wall 1991; Lam and Wilson 1992; Postiff et al. 1998], and there are limits to the extent to which practical architectures can find available parallelism (e.g., instructions with no dependency between them may be relatively far apart). A problem that has arisen more recently is that the increasing complexity required for more aggressive ILP has a high cost in energy use [Yeap 2002] and hence also heat.

Another limitation to pursuing performance using more and more aggressive ILP with higher and higher clock speeds is the growing gap between the speed of CPUs and DRAM, resulting in limited gains as a higher fraction of the CPU's time is spent waiting for DRAM, a problem called the *memory wall*, predicted in 1995 [Wulf and McKee 1995].

## **Multiprocessor and Multicore**

In the past multiprocessor architectures differed widely in characteristics. Some emphasised data parallelism (the same instructions on several or many different data items in registers or memory), others instruction parallelism (different instruction streams on each ALU). Memory organization also varied. A distributed-memory architecture had no shared memory and communication primitives like messaging were used. A shared-memory architecture had one global memory and required mechanisms to ensure consistency of caches. A distributed shared memory system [Bennet et al. 1990; Dwarkadas et al. 1993; Bordawekar 2000] is physically distributed but gives programmers as model that looks like shared memory. There are also programming tools and libraries like MPI that hide some of the detail of the memory model, but some understanding of the memory model is essential to achieve performance.

More recently, as limits of ILP and scaling up the clock speed (in part because of the memory wall but also because of limits to ILP and the increasing cost of hot high-energy consumption designs), multicore designs have become popular, and these generally are shared-memory designs, often with a shared lower-level cache. Writing parallel code is now an option for the mass market, so the specialist skills needed for programming big iron in the 1990s [Cheriton et al. 1991, 1993; Machanick 1996] now apply more widely, but the problems are no easier. A good understanding of how the memory system works in shared-memory multiprocessors is even more important to achieving good performance than with a uniprocessor.

## **GPUs**

The conversion of specialist processors designed for graphics to general-purpose computing is not a new idea. The Intel i860, marketed as a general-purpose CPU with graphics support [Grimes et al. 1989] was clearly designed more with graphics support than general purpose use in mind. Among other things, it suffered very high latency for context switches, and VM support is minimal. On a page fault, it only reports that a fault occurred, not whether it's a read, write or instruction fetch, meaning the page fault handler has to reconstruct the cause, in effect interpreting the instruction that caused the fault to work out what happened [Anderson et al. 1991]. The i860 was reasonably successful as a graphics processor in the days when a high-end graphics system was a multichip design, with features presaging vector extensions to the IA32 line. Overall the i860, despite being deployed on some large-scale supercomputer designs [Berrendorf et al. 1994], was not a great success as a high-performance CPU.

So is the general purpose GPU (CPGPU) concept reasonable, given that specialist processors have not historically been a win? There are arguments for and against. Against, Amdahl's Law tells us that a  $100 \times$  speedup of a small section of our code will have a small overall effect on run time, and coding for these specialist processors, even with high-level tools like Nvidia's Cuda [Wynters 2011]<sup>2</sup>, is hard. What's more these toolkits tend to be vendor-specific. On the for side, the massive market for GPUs means that there's a lot more critical mass behind this movement than other attempts at using specialist processors for more general purposes than originally intended. Computers with powerful GPUs are increasingly ubiquitous in the mass maket, making it at least possible that massive-scale computation using such GPUs will continue into the future, whereas past specialist designs did not have that critical mass.

$<sup>^2</sup>$ More at http://developer.nvidia.com/nvidia-gpu-computing-documentation.

Architecture Areas 15

# Warehouse-Scale Computing and the Cloud

One of the ongoing debates in computer architecture is whether large-scale computing is best achieved with massive numbers of inexpensive boxes with redundancy designed in, or dedicated highly-scalable designs. One of the earlier ideas of this type is *RAID*, originally *redundant array of inexpensive disks* [Patterson et al. 1988] (now usually "independent" instead if "inexpensive", possibly so manufacturers can claim their disks are "enterprise grade" and hence not inexpensive).

Possibly the best-known example of the extension of this idea to a *redundant* array of inexpensive computers (no one uses RAIC as a name for some reason) is Google's approach or warehouses full of inexpensive computers, with many fail-safes to allow for hardware and software faults [Barroso et al. 2003]. This kind of infrastructure is becoming increasingly important as the Internet expands to ever new services including some that might for a brief period require hundreds or even thousands of servers, then settle back to more modest requirements [Liu and Wee 2009]. How best to put these services together is still a work in progress, and there is no doubt that expertise in this field will be useful for some time ahead.

The "cloud" term is somewhat vague in meaning, and is really marketing speak for distributed services, sometimes storage, sometimes computation, sometimes both. The key feature of a *distributed* system, as opposed to a *networked* system, is naming or location *transparency*, i.e., you don't know (or need to know) whether data or a process is running locally, over a network or even over several computers – that is a performance detail. By contrast, a networked service requires naming the location where the service occurs. What really distinguishes the cloud from earlier distributed services is that the infrastructure is provided on a closed proprietary system, rather than as a file system or operating system that installs on your own computer. While some such services like Google Drive or DropBox occupy file space on a computer on which you use the service, they do not integrate cleanly. Can you put a DrobBox folder into a Google Drive folder? If so, will this still work next week? Can you mix any of these with Amazon's AWS or Apple's iCloud?

Large-scale cloud services are linked to warehouse-scale computing in that they need large highly-scalable geographically dispersed implementations. That's not to say all implementations use the same infrastructure, or that someone won't find a better way. This is a relatively new area and one with a lot of potential for innovation – even though the core concept of a distributed system is quite old, with some of the theory dating back to the 1970s [Lamport 1978].

# 1.5 The Other Edge

Much of the previous discussion assumes we want the fastest possible system, constrained by cost, power consumption etc. However, Moore's Law can be read the other way. As hinted at by Gordon Bell, new classes of computer become viable as a given level of functionality becomes available at a price point [Bell 2008].

In the 1970s, a personal computer capable of doing interesting work – including the first spreadsheet, VisiCalc [Bricklin and Frankston 1979], became viable because a single-chip microprocessor powerful enough to run an elementary operating system and programming tools reached an affordable price point.

Since then, other breakthroughs have included:

- *scalable PC* the original IBM PC was not a huge advance on the previous generation but Intel's ability to add enhancements like 32-bit addressing as new thresholds in the number of affordable transistors were crossed meant the CPU remained viable even if major OS rewrites and recompiles were needed in the transition to 32 bits (and less so to 64 bits)

- Linux when the IA32 became powerful enough to support a UNIX-like operating system it was only a matter of time before a free UNIX emerged; Linux was the first (1991) but there are others like FreeBSD (which appeared only two years later)

- *RISC* the ability to implement a version of Seymour Cray's 1960s ideas on a single chip, starting from the 1980s, culminating in the collapse of most medium to large-scale computing options that didn't use microprocessors

- mobile devices starting from increasingly sophisticated notebook computers, mobile devices today include smart phones and tablets. Each new form factor derives from another step in the amount of functionality available at a lower price point and able to run longer between charges or on a smaller and hence cheaper battery

- *pico-PCs* a likely development out of smart phone parts is ultra-small PCs, of which the Raspberry Pi is an example

In some ways the "other edge" space is even more exciting than the big iron end of the design space because it creates the potential to transform the lives of many people, always remembering that technology is only a tool, and a tool only works if competently applied and to the right problem.

Structure 17

# 1.6 Structure

In the remainder of this course I examine the above topics in more detail. First, I use memory hierarchy as a starting point for understanding quantitative principles of system design and research, as well as trends and how to analyse their long-term effects. Next I examine parallelism in its various forms, starting with instruction-level parallelism. This is a large topic on its own encompassing pipelines, out of order execution, minimizing delays from branches and the rationale behind the multicore movement. Next I look at alternative models of parallelism including data parallel architectures and more specifically GPUs. I examine thread-level parallelism and how it relates to areas previously covered including memory hierarchy and multicore designs in the multiprocessors chapter, and review features of traditional vector machines as a contrast to multimedia extensions and GPUs. Finally I look at the two ends of the scale: warehouse-scale computing and emerging small-scale systems as representing two very different consequences of technology trends, the smaller devices included in discussion of how to understand and take advantage of trends.

The material covered is loosely based on Hennessy and Patterson [2012] with additions based on my own experience and research.

# **Exercises**

- 1. In terms of a programmer's view, how do ILP and thread-level parallelism differ?

- 2. How big is the gap between a RISC architecture and a typical high-level language? Does an instruction set primarily composed of loads and stores, ALU operations and branches fit a wide range of languages?

- 3. Is it possible to have a program with good temporal locality but poor spatial locality? Is the opposite scenario, good spatial but poor temporal locality possible? Explain.

- 4. Why do multicore designs still have relatively aggressive pipelines, with over 100 instructions in consideration at any one time, register renaming and out of order execution?

# 2 Memory and Quantitative Design

EMORY HIERARCHY is a critical part of computer system design because a memory large enough to contain a whole program and its data, and also fast enough not to stall the CPU, in most cases would be prohibitively expensive and almost certainly physically impossible to design. While we can rely on the principle of locality as outlined in Chapter 1 in general terms, we cannot set the size and organization of the various layers of the memory system with reasonable precision (achieve a required cost-performance trade-off) without measuring variations.

In this Chapter, I present a range of design alternatives and techniques for measurement focused on evaluating the design alternatives for memory. These same techniques can apply with differences in detail to measuring differences in design alternatives in other areas of system design.

# 2.1 Memory Systems

Memory systems encompass the biggest range in performance difference of any one logical component of a computer system. For this reason, there are different organization details at each layer, though there are common principles. First I present these common principles, then illustrate how they apply at each level.

# 2.1.1 Organization Principles

Aside from obvious classifications like speed, size and cost, memory systems are generally organised by how they can be accessed and managed. The following in general terms apply to all memory systems, with significant variations in the detail (summarised in Table 2.1):

naming – some kinds of memory have unique names (generally this applies to registers), others use an addressing scheme where a location is identified Memory Systems 19

| term          | definition                                                          |  |  |  |

|---------------|---------------------------------------------------------------------|--|--|--|

| block         | unit of storage or management                                       |  |  |  |

|               | caches: also called line                                            |  |  |  |

|               | VM: fixed-size page (older systems had variable-sized segments)     |  |  |  |

| hit           | block is found at the requested level                               |  |  |  |

| miss          | block is <i>not</i> found at the requested level                    |  |  |  |

| replacement   | if there is no vacant block to place a miss another must be evicted |  |  |  |

| victim        | tim block to be replaced                                            |  |  |  |

| dirty         | block modified with respect to one or more lower layers             |  |  |  |

| write through | writes reflected at next layer down                                 |  |  |  |

| write back    | dirty block copied only on replacement                              |  |  |  |

| associativity | measure of how many different locations a block can occupy:         |  |  |  |

|               | direct-mapped: only 1 location for any block                        |  |  |  |

|               | n-way set associative: n different locations for a block            |  |  |  |

|               | fully-associative: a block can be placed anywhere                   |  |  |  |

**Table 2.1:** Common terminology. There is some variation across layers but these terms generally apply.

by a numeric offset from the start

- accessible unit some kinds of memory are accessible in fixed-size units (again, mostly registers, though some have variants like single and double precision) whereas others can be accessed at various granularities such as a byte, two bytes, etc. The latter category may have alignment restrictions (e.g., if memory addresses refer to bytes, a two-byte access must start at an even address) and preferred sizes (a machine word is usually the width of the data bus)

- *transfer unit* some kinds of memory only transfer to the next layer up or down in fixed size units (e.g., a cache typically has a *block*, sometimes called a *line* of fixed size; a VM system has a usually fixed page size)

- management unit some kinds of memory are managed in fixed size chunks, including issues like protection, recording whether the contents is modified (sometimes called dirty), valid meaning that the unit of memory can be used without generating an interrupt, present meaning that the unit of memory is available at that level of the hierarchy or shared, meaning that more than one way exists to access that memory (usually a property of multiprocessor systems)

• replacement – how do we determine which unit to evict if we run out of space? If we do so, what is the policy on writing dirty data to the level below?

As we examine levels of the hierarchy we will see how these properties apply and differ. Computer architects consider faster elements of the hierarchy to be "higher" and if the same kind of memory is split into more layers, the highest level is numbered 1.

# 2.1.2 Levels of the Hierarchy

In considering levels of the hierarchy, it is logical to start from the top and work down. When a program starts executing, the first thing that happens is the program counter (PC) register is loaded with the start address (actually the last thing from the point of view of the software that loads the program). The ALU then attempts to fetch the instruction from the next level down, the L1 cache – but only after translating the address (on a VM machine) using the TLB, a level above the L1 cache in terms of speed. Levels below these are only accessed if the required data, page translation or instruction is not available at the topmost level. For this reason I describe the hierarchy from the top (fastest) down, though I defer discussion of some of the more complex strategies to the lower layers, since the interface between the very slowest layers and the next level up justifies sophisticated strategies to minimise access to the slowest levels of the hierarchy.

## **Registers**

The top level of the hierarchy is registers. Registers are tightly integrated into the ALU and pipeline, and can usually be accessed in a fraction of a clock cycle. In terms of our universal principles:

- *naming* register names are encoded into machine instructions, and generally can't be computed at run time

- *accessible unit* registers are a fixed size though they may sometimes support precision variations (e.g., single, double)

- *transfer unit* registers only transfer values in fixed sizes up to their widest precision

- management unit registers are sometimes collectively managed in hardware, e.g., if there is hardware support for multithreading, each hardware context has its own copy of the registers. More commonly detailed management of registers is in software: the compiler manages what is within

Memory Systems 21

them within a single process, and the OS manages saving and restoring registers between context switches (some older designs have hardware support for context switches)

• replacement – deciding which register to spill is usually totally under software (in practice, the compiler or on a context switch, the operating system) control

#### TLB

The next level of the hierarchy is the *translation lookaside buffer* or *TLB*, which contains recent page translations. The TLB is usually integrated into the pipeline and can be accessed in a fraction of a clock cycle. A TLB is often organised as an *associative memory*, in essence a hardware hash table that doesn't have collisions. The key being looked up is effectively the address: in this case, the virtual page number. A TLB is in the critical path of logic: if a page translation can be found, it is used immediately to check if the memory location is represented in the L1 cache. In some architectures, virtually addressed caches [Inouye et al. 1992; Wheeler and Bershad 1992] are used, making TLB speed less critical, possibly completely eliminating the need for a TLB [chan Kang et al. 2011].

- naming virtual page numbers identify entries

- *accessible unit* each item in the table is a pair: a virtual page number (to check compare against when indexing) and a physical page number

- *transfer unit* the TLB is generally filled and replaced in units of 1 page translation though it is possible to flush it (depending on the system, this may be necessary on a context switch)

- management unit as with transfers TLBs are usually managed per entry. With a virtually-addressed cache, if a TLB is present, it will need to be tagged with process IDs or be flushed on a context switch

- replacement TLB replacement can in theory encompass the range of possibilities used in page replacement polices (see below: least recently used, first in first out, etc.) but in practice since the TLB is in the critical path for performance, a strategy that is fast to implement such as random replacement has some appeal

Any machine that is designed to achieve reasonable performance with VM needs hardware support for page table lookups to speed up handling TLB misses [Jacob and Mudge 1998]. For example, Intel's IA32 architecture has a hardware page table

walker that assumes a 2-level page table, reducing the time to handle a TLB miss to data references and no code in routine cases. Hardware page table walkers limit OS designers' ability to experiment with new strategies for page table design. In the worst case, a page table lookup, even with hardware support, can involve a trip to backing store, since some systems allow parts of the page table to be swapped out.

Minimising TLB misses is an aspect of performance tuning that is often neglected, and the consequences can be high. Assume an average TLB miss adds 50 cycles execution time (miss penalty). That is not an unreasonable assumption given the cost of accessing DRAM vs. CPU cycle time. Then if 1% of instructions result in a TLB miss on a machine that would otherwise execute 1 instruction per clock cycle, average execution time becomes

$$t_e = 1 + 0.01 \times 50$$

or 1.5 cycles, a significant drop over 1 cycle per instruction.

How can a high TLB miss rate be avoided?

A TLB represents one page translation. If you have a memory access pattern that spends very little time on one page, you will access many pages without accessing a high fraction of total memory. For example, if a page is 4KiB (the most common size), and you have a loop that looks like this:

for (i = 0; i <

$$1024 * 1024 * 1024$$

; i+= 4 \*  $1024$ )

a[i] = 42;

each assignment is on a different page. This is of course a contrived example, but it's possible to write code that scatters data references around memory if not in quite such an extreme way. For example, object-oriented code with many small objects that are not referenced in the order they are placed in memory can exhibit this problem [Machanick 1996].

# Caches

The next level of the hierarchy is caches. A cache is usually made of static RAM (SRAM), which uses transistors as its building blocks and hence draws on the same technology advances as CPUs. SRAM does not have any significant delay for an access over and above than the time to transfer its contents, so there is no special advantage to doing access in large units. A wide bus will deliver contents faster than a narrow bus because it can do so in fewer transactions, but there is no lengthy setup time to amortize.

The top-level (level 1, or L1) cache is usually in recent designs tightly integrated into the pipeline and can be accessed in one clock cycle. To continue

Memory Systems 23

with our logical progression down the hierarchy, I describe caches before virtual memory, though VM is the natural place to describe some of the more complicated strategies since VM is closer to the operating system and hence has a higher software component.

- naming cache contents is generally tagged with a value representing the machine address of the cache block

- accessible unit when accessing a cache, the CPU uses the same units of addressing as apply to main memory

- *transfer unit* caches contents are moved or copied in blocks (also called lines) that are typically multiple machine words long. Typical values are 32 to 128 bytes. Some caches feature *critical word first*, in which the part of the block that caused the miss is transferred first to reduce the time the CPU is stalled [Zivkov et al. 1994; Moudgill et al. 1999; Aasaraai and Moshovos 2010]

- management unit most caches have tags representing the address of the contents and state (modified, valid, etc.) for each block

- replacement cache replacement policy depends on how the cache is organized:

- direct-mapped a given address can only go into one location so if that location is already occupied, whatever is there is replaced: very simple to implement

- n-way set associative a given address can go in one of n locations, so if none of those is available, one has to be selected for replacement; given the relatively high speeds involved cache replacement strategies tend to be simple, though some have investigated software-based approaches [Cheriton et al. 1986] that approach the sophistication of virtual memory page replacement; for small n, hardware is still reasonably simple

- fully associative some have proposed making the lowest level of cache look more like virtual memory, and hence advocate approaches that approach the sophistication of virtual memory page replacement [Machanick et al. 1998; Hallnor and Reinhardt 2000], including allowing a cache block to be placed anywhere in the cache: to implement full associativity purely in hardware is expensive and impractical for a large cache since every location has to be searched to compare the address tag with the request

**Figure 2.1:** Cache addressing. The low-order bits of the address are used to find the right byte or bytes within the cache block. The next-lower bits are used as an index into the cache, and the high-order bits in excess of those needed to identify a cache block are stored in the tag to identify which of the possible blocks is actually in the cache. For higher associativity, cache indexing produces more than one result and a hit is detected by checking if any of the stored tags matches the required block.

In Figure 2.1 I illustrate how a machine address is broken up to check for a hit in a cache. In the event a hit is found, the cache returns the required memory items (or in the case of a write, overwrites the portion of the cache block pointed at by the address). In the case of a miss, the cache controller must identify a victim (in a direct-mapped cache (2.1(a)), that's always the same location; in other organisations (2-way associative, 2.1(b)), a victim may be picked at random since time is short at this level of the hierarchy), and request the block from the next level down. If the victim block is *modified* (or *dirty*), it must be written back to the next level down (*cleaned*). Caches can have one of two write policies:

- write through all writes immediately are reflected at the next level down: seldom used because memory traffic is high

- write back a dirty block is cleaned on replacement

In addition to the address tag, cache blocks have status bits. These can vary but common examples include:

- modified a bit indicating the block is dirty

- exclusive a bit indicating the block is not shared with another CPU or core

- shared a bit set if the block is shared across more than one CPU or core

- invalid a bit set if the block does not have valid contents

A system with this exact set of states (not necessarily that number of bits) is referred to as using the  $MESI\ protocol^1$ . You may wonder why you need a

<sup>&</sup>lt;sup>1</sup>A few other details, specifically restrictions on the allowed combinations, apply to the definition of MESI.

Memory Systems 25

shared and an exclusive state. If a block is not initially shared, setting it exclusive makes this clear. We go more into shared caches when considering multiprocessor systems (Chapter 4).

In most systems currently available, there is more than one level of cache. The L1 cache is relatively small and tightly integrated into the ALU so it can keep up with the pipeline. The L2 cache is larger and not as fast; some systems have 3 or even more levels of cache, on the principle that as much cache as possible is good but a large one cannot be fast without high costs in energy, a significant factor in design.

In aggressive ILP designs, a cache miss can cause a major slowdown. With a clock speed of 2GHz, one cycle is  $0.5\mu s$ . If you can execute 4 instructions on one clock, the average time per instruction is  $0.125\mu s$  so even if your second-level cache is very fast with hits taking only  $1\mu s$ , a miss costs a delay of 8 instructions. To address this problem, non-blocking caches allow any instructions that are ready to go to continue without waiting for a cache miss [Chen and Baer 1992; Belayneh and Kaeli 1996; Aasaraai and Moshovos 2010]. If your ILP design already includes out of order execution, likely with an aggressive design, support for non-blocking caches is a relatively cheap addition.

For multicore systems, a common approach is to have an L1 cache that is local to each core and a shared L2 cache. Shared caches is an idea explored in research into high-end systems in the past [Cheriton et al. 1988, 1989; Nayfeh and Olukotun 1994] – illustrating the value of a thorough understanding of technology history as technology change makes it possible to package old high-end ideas at new affordable price points.

#### **Main Memory**

The main memory in current systems is generally made of DRAM. DRAM uses a capacitor as its storage element. Unlike SRAM, DRAM has to be refreshed periodically because a capacitor's charge drains. Because the underlying technology is different, DRAM has its own price-performance trend, and that is driven more by price per bit than by speed. Hence, DRAM speed improvement lags CPU speed improvement (less so since the move from aggressive ILP and higher clock speeds to multicore, but multicore designs still are growing faster than DRAM speed, if you aggregate the rate at which memory requests occur across the cores). Also unlike SRAM, there is a lengthy delay before the contents can be accessed, so most current DRAMs have streaming modes where, once an access is set up, further sequential accesses moving along from that location are a lot faster. For this reason, moving to or from DRAM in large units is attractive if it does not cause other delays.

- *naming* a memory address usually refers to a byte, numbered from the start; many machines require aligned access for large units (e.g., to do a 2-byte access, you must start on an even address)

- accessible unit most DRAM systems are accessible at the byte level though

in practice to handle cache misses, write-backs and write-throughs, a larger

unit is transferred

- *transfer unit* the transfer unit is the same as the access unit in practice, since most DRAM access are via the cache.

- management unit at the low level, DRAM can be managed down to the byte level but in practice, with a VM system, what is in the DRAM or not is managed in pages

- replacement replacement strategy in VM is complex and must take into account the mix of processes, other IO (since paging uses an IO device) and the extremely high latency of backing store. Some strategies include:

- least recently used or LRU the page used longest ago is evicted

- first in first out or FIFO the oldest page is evicted

- working set or WS each process is limited to pages it used over some fixed time period

- clock a way of approximating LRU by systematically marking pages as unused, working around the list of pages in the style of a clock hand, and selecting a victim that is not marked as used (indicating the page was not used since the clock hand last passed that page)

- page standby list a list of pages recently target for eviction [Russinovich 2007]

In some systems there may be a mix of *global* and *local* policies: a global policy balances DRAM use across processes, while a local policy attempts to ensure that a given process has enough DRAM to make progress. A local policy generally attempts to implement the *working set* principle: a process generally only access a subset of its pages for a reasonably long time before shifting to another part of its code or data address space. While the working set concept is quite old [Denning 1968], the principle still applies and will as long as memory has a hierarchy with several orders of magnitude difference in speed. A global policy may sometimes simply shut down processes if there is insufficient RAM (in the worst case, terminate them).

Memory Systems 27

A complete coverage of virtual memory properly belongs in an operating systems course since it's at the interface between hardware and software, and software plays a much larger role than in higher levels of the hierarchy.

#### **Paging Device**

Paging devices historically have been mechanical magnetic storage devices of various forms. Early paging devices were dedicated magnetic *drums*, conceptually the same as a disk but with the recording surface on the outside of a cylinder. The earliest commercial VM system, the British Ferranti Atlas [Lavington 1978], had a drum memory with rotational time of 12ms (and thus an average rotational delay of 6ms), and no seek time since the heads were fixed, making it competitive with technology of 50 years later on speed if not capacity. The basic cycle time of the CPU was  $2\mu$ s, only about  $10^3$  faster, compared with today's speed gap of a factor of over  $10^6$ . It is the observation that in the late 1990s the delay in handling a cache miss to DRAM was approaching 3 orders of magnitude slower than CPU cycle times that led me to starting the RAMpage project, in which I move the virtual memory system up a layer to handle misses from SRAM to DRAM [Machanick et al. 1998] – so knowing a bit of history is useful.

Today paging is usually on standard disks. There are two major variants: the traditional UNIX approach of a swap partition, and using free space in the boot partition. Mac OS X uses the latter; Linux can use either. On iOS devices, which usually use flash instead of disk, paging is limited to evicting easily recreated content such as code from RAM. There are two reasons for this strategy: flash is small on these devices compared to a disk, and repeated modification of the same bits in flash can wear them out. Programmers of iOS apps are advised by Apple to accept low memory messages and reduce their memory footprint as required [Apple 2012]. Other types of device (including Apple's notebook line) use flash instead of disk and do use flash for paging; reducing the tendency to wear out overused bits using *wear levelling* [Chang 2007] may be easier with Apple's strategy of sharing the file system with backing store rather than using a separate swap partition.

- naming a page on backing store can be anywhere on the device and is identified by a page table, using the virtual address (or more properly the virtual page number) as an index

- accessible unit a VM system usually deals in whole pages

- *transfer unit* pages may be transferred singly or the OS may move several contiguous pages to reduce overall latency

- management unit pages are managed as a unit but also by process; if a process completes or dies, all its pages are freed

- replacement since this is the bottom of the hierarchy, there is no replacement until a process exits the system; however, some systems do not keep pages on backing store if they exist in RAM and in that sense pages may not always exist on disk.

In a difference to cacheing terminology, a miss is called a *page fault*. In most real systems, a page fault results in a *context switch*: there is no point stalling the CPU for millions of cycles so despite the fact that a context switch has other significant costs like losing contents of caches, it is faster overall to allow another process to use the CPU while waiting for a page fault to be processed.

Having wended our way all the way down from the world of registers and TLBs that are accessible in a fraction of a clock cycle to paging devices that area accessible in millions of cycles, let's see how we measure the effects of all of this.

#### 2.2 Measurement

There are many levels at which we can measure computer systems performance. We can measure individual components, we can measure times taken by small blocks of code, we can time a whole program, and we can time a workload of interest. Aside from timing overall, we can apportion costs, so as to work out what to improve. Then in addition to timing, we can measure other attributes of interest like energy use, memory requirements if we change some detail (e.g. simplify the instruction set) and frequency of use of specific features.

#### 2.2.1 Architecture-Oriented Measures

Depending on what we are measuring and how much detail we want, there are many variations, including:

- logic-level simulation useful for checking design details like timing and energy use, but too slow to measure non-trivial program runs though work on speeding up such simulations may make larger runs viable [Chatterjee et al. 2009; Mironov et al. 2010]

- execution-driven simulation a program runs on a simulator which can measure at a particular (sometimes parameterizable) level of detail including

- cycle-accurate simulation simulation run in software designed to give an accurate representation of machine time or energy use [Simunic

Measurement 29

et al. 1999]; slow for large runs though recent enhanced techniques make such methods more viable for whole workloads [Lee et al. 2008]

- whole-system simulation while not necessarily cycle-accurate, these simulators are fast enough to evualate whole workloads