# MIPS2C

programming from the machine up

Philip Machanick

C part omitted from this printing

MIPS2C: PROGRAMMING FROM THE MACHINE UP First edition, 2015 Minor corrections: March 2017, April 2019, October 2020 – reformatted without C March 2018 Copyright © Philip Machanick 2014, 2015, 2016, 2017, 2018, 2019, 2020

Published by Philip Machanick in the RAMpage Research imprint under an Attribution-NonCommercial 4.0 International (CC BY-NC 4.0) licence:

http://creativecommons.org/licenses/by-nc/4.0/ The quick summary: free to use however you like but not for commercial purposes.

**SPIM documentation**: Appendix E is copyright to the author as indicated on the first page and using this material does not imply endorsement by James Larus of this book.

**Picture credits**: all illustrations are either by the author or from public domain sources, as acknowledged in the text.

| Publication details  | apply to full version with C                               |

|----------------------|------------------------------------------------------------|

| Author:              | Machanick, Philip, 1957-                                   |

| Title:               | Mips2C: programming from the machine up / Philip Machanick |

| Edition:             | 1st ed.                                                    |

| Publisher:           | Grahamstown, South Africa : RAMpage Research, 2015.        |

| ISBN:                | 978-0-8681048-7-4 (pbk.)                                   |

| LoC classification : | QA76                                                       |

**Note**: this printing differs slightly in layout and omits the C section so do not cite with ISBN.

Last typeset 27 October 2020

# Preface

W THIS BOOK? Some years ago I took part in a panel discussion titled "Programming Early Considered Harmful" at the SIGCSE 2001 conference [Hitchner et al. 2001]. Once of those present was Yale Patt, whom I had met briefly on a sabbatical at University of Michigan, where he was at the time a professor working in computer architecture. His role on the panel was to proselytise his book, *Introduction to Computing Systems: From bits & gates to C & beyond* [Patt and Patel 2013], which introduced programming from the low level up. I found the idea intriguing particularly as I also was concerned with the problem that students tend to stick with the first thing they learn. If my concern was correct, it should be better to start with machine-level programming. Nonenetheless, I am always open to new ideas, and when the opportunity presented itself to run a computer organization course followed by a C course, I decided to try the idea for myself.

After reviewing the latest edition of Patt and Patel [2013], I saw a gap for a treatment that focused more on assembly-level programming as it relates to C, and less on the hardware. For any who disagrees, there is another book out there.

Another problem is that text books are becoming increasingly expensive. Patt and Patel [2013] retails for over \$150; the fifth edition of the classic *Computer Organization and Design: The Hardware/Software Interface* [Patterson and Hennessy 2014] lists at almost \$90.

That takes me to another motivation for writing this book: affordability. Where I live, South Africa, we are charged European prices for books. While publishers do sometimes try to lower prices when we ask nicely, books are very expensive in relation to earning power. We also have a significant fraction of students from very low income groups. All of that motivates me to explore ways of pushing cost down. One way I am doing that is by publishing this book with a Creative Commons Attribution-NonCommercial license, which makes it free to copy for non-commercial purposes. Another way I aim to bring costs down is by publishing using print on demand (PoD). The cost per book printed using PoD publishing is higher than the cost per book of a large print run, but a large print run is only economic if a significant fraction of the books is sold. By using PoD, I can also cut out the overheads of a publisher, who has to make money out of successful books to pay for warehouses full of unsuccessful titles.

How well does it work?

My students do this course after a year of object-oriented programming so it is not in that sense a low-level first approach. They find it hard to break out of calling functions "methods", as an example of an entrenched habit. Overall though my experience is that the approach works. To some extent starting with a relatively high-level language with classes and objects makes it easy to code things that provide tangible results. Taking a dive after that into the low level is a bit discomforting, but so is any real learning.

A few thoughts on my approach.

Standard MIPS-based treatments generally follow a particular standard for compiler calling conventions; I construct my call stack slightly differently for two reasons. The first is I find my approach a bit easier to explain. The second is to get across to students that the stack is not a fixed structure in memory, but the consequence of conventions that you can change.

I try to avoid teaching things in a way that has to be undone later. Rather, I use simplifications, then fill in the gaps. For example, I introduce templates for coding statements into assembly language (such as **if** statements or **for** loops) without taking into account all the requirements for generality, then add in those requirements.

I use C as a "pseudocode" deliberately in the first part of the book, even though C is clearly a real language, to create familiarity with the syntax. For students with a background in a C-like language, this should not present a major issue. For others, the "pseudocode" is mainly used in small examples and should be understandable from the context.

My intent is to put students in a position to understand topics like compilers, recursion and data structures by seeing what happens underneath. I think the approach works, though the best test is whether graduates who have learnt this way are able to work more efficiently and with more insight later in life.

Finally, I look forward to hearing from others who use this material. If you choose to use the free version, your views will be just as valuable as if you pay for a commercially published copy.

# Contents

| Pr  | eface   |                                             | i  |

|-----|---------|---------------------------------------------|----|

| Lis | st of H | ligures                                     | vi |

| Lis | st of 7 | ables                                       | ix |

| De  | finitio | ons                                         | X  |

| 1   | Intro   | oduction                                    | 1  |

|     | 1.1     | Some Basics                                 | 3  |

|     | 1.2     | Machine Language versus High-Level Language | 5  |

|     | 1.3     | Code Translation                            | 8  |

|     | 1.4     | Machine Instruction Sets                    | 10 |

|     | 1.5     | The Machine                                 | 12 |

|     | 1.6     | Practicalities                              | 15 |

|     | 1.7     | Further Reading                             | 17 |

|     | Exer    | cises                                       | 17 |

| 2   | Num     | bers and the Machine                        | 19 |

|     | 2.1     | Logic                                       | 19 |

|     | 2.2     | Numbers                                     | 25 |

|     | 2.3     | Numbers and Logic                           | 34 |

|     | 2.4     | The Machine                                 | 37 |

|     | Exer    | cises                                       | 46 |

| 3   | Asse    | mbly by Example                             | 48 |

|     | 3.1     | Instructions and their Formats              | 48 |

|     | 3.2     | Memory access                               | 52 |

|     | 3.3     | ALU operations                              | 60 |

|    | 3.4   | Control                            | 67  |

|----|-------|------------------------------------|-----|

|    | 3.5   | Floating Point                     | 73  |

|    | Exer  | cises                              | 75  |

| 4  | Men   | nory and Functions                 | 78  |

|    | 4.1   | Calling functions                  | 81  |

|    | 4.2   | Global Variables                   | 91  |

|    | 4.3   | Local Variables and the Call Stack | 96  |

|    | 4.4   | Bigger Parameters                  | 110 |

|    | 4.5   | Recursion                          | 112 |

|    | Exer  | cises                              | 119 |

| 5  | Data  | 1 Structures                       | 122 |

|    | 5.1   | Machine-Level Data                 | 122 |

|    | 5.2   | Arrays                             | 125 |

|    | 5.3   | Dynamic Data                       | 142 |

|    | 5.4   | Structured types                   | 149 |

|    | 5.5   | Objects                            | 159 |

|    | 5.6   | Putting it all Together            | 167 |

|    | Exer  | cises                              | 168 |

| 6  | Perf  | ormance                            | 171 |

|    | 6.1   | More at once                       | 172 |

|    | 6.2   | Memory Hierarchy and Performance   | 180 |

|    | 6.3   | Input and Output                   | 183 |

|    | 6.4   | Energy and mobility                | 185 |

|    | 6.5   | Wrap-up                            | 186 |

|    | Exer  | cises                              | 187 |

| Re | feren | ces                                | 190 |

| A  | ASC   | II Character Set                   | 192 |

| B  | MIP   | 'S Register Conventions            | 195 |

| С  | SPIN  | M System Calls                     | 197 |

|    |       | M Call Stack                       | 199 |

iv

# CONTENTS

| Ε | SPIN | A Backg | ground                              | 201 |

|---|------|---------|-------------------------------------|-----|

|   | E.1  | SPIM    |                                     | 202 |

|   |      | E.1.1   | Simulation of a Virtual Machine     | 203 |

|   |      | E.1.2   | SPIM Interface                      | 203 |

|   |      | E.1.3   | Surprising Features                 | 203 |

|   |      | E.1.4   | Assembler Syntax                    | 204 |

|   |      | E.1.5   | System Calls                        | 206 |

|   | E.2  | Descrip | ption of the MIPS R2000             | 208 |

|   |      | E.2.1   | CPU Registers                       | 208 |

|   |      | E.2.2   | Byte Order                          | 211 |

|   |      | E.2.3   | Addressing Modes                    | 211 |

|   |      | E.2.4   | Arithmetic and Logical Instructions | 212 |

|   |      | E.2.5   | Constant-Manipulating Instructions  | 214 |

|   |      | E.2.6   | Comparison Instructions             | 214 |

|   |      | E.2.7   | Branch and Jump Instructions        | 215 |

|   |      | E.2.8   | Load Instructions                   | 217 |

|   |      | E.2.9   | Store Instructions                  | 217 |

|   |      | E.2.10  | Data Movement Instructions          | 218 |

|   |      | E.2.11  | Floating Point Instructions         | 219 |

|   |      | E.2.12  | Exception and Trap Instructions     | 221 |

|   | E.3  | Memor   | y Usage                             | 222 |

|   | E.4  | Calling | Convention                          | 222 |

|   | E.5  | Input a | nd Output                           | 223 |

### Index

226

# **List of Figures**

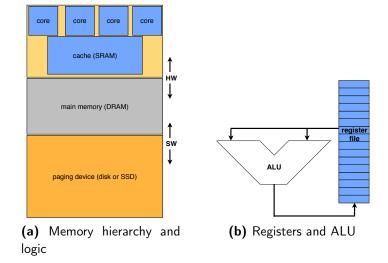

| Major components of the memory hierarchy and CPU 13    |

|--------------------------------------------------------|

| Multilevel caches in a multicore deisign               |

| A nand gate used to implement a not gate               |

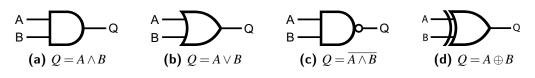

| Logic gate symbols                                     |

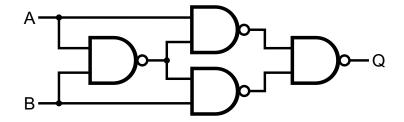

| Exclusive or from nand gates                           |

| IEEE 754 32-bit floating point         30              |

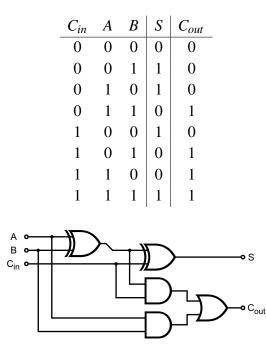

| Half adder logic                                       |

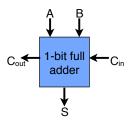

| Full adder logic block                                 |

| Full adder logic circuit                               |

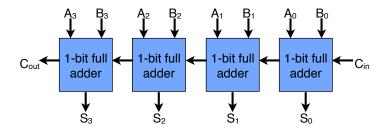

| Four-bit adder block diagram                           |

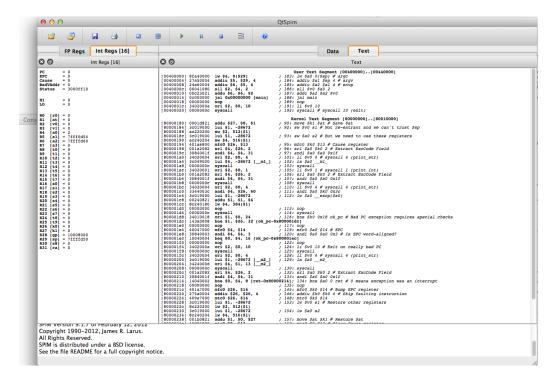

| SPIM at launch                                         |

| SPIM user text segment at launch                       |

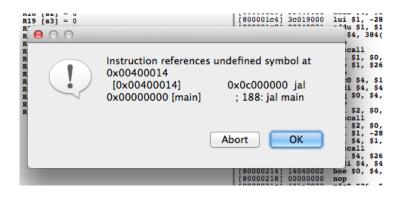

| SPIM upset about no main entry point                   |

| SPIM user text segment: minimal program                |

| SPIM user text segment: for loop                       |

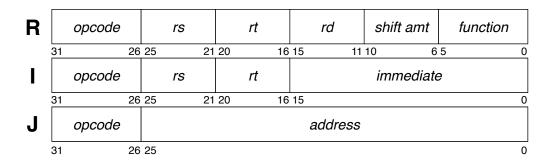

| MIPS common instruction formats                        |

| MIPS load upper immediate instruction 51               |

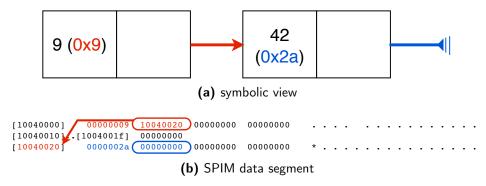

| SPIM data segment                                      |

| SPIM data segment: intialized                          |

| SPIM text segment: loads from memory                   |

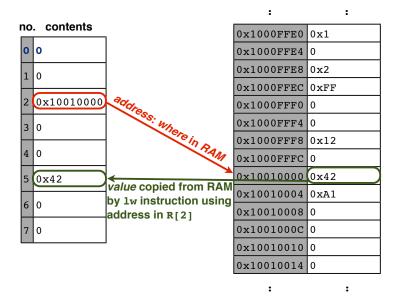

| Registers vs. RAM                                      |

| SPIM text segment: more efficient loads from memory 58 |

| SPIM data before and after saving SP                   |

| Sign-extending                                         |

| Effect of short loads                                  |

| SPIM data layout with a short data item                |

|                                                        |

| 3.12                                                                                                                                                                      | SPIM expansion of <b>mulo</b> pseudoinstruction                                                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

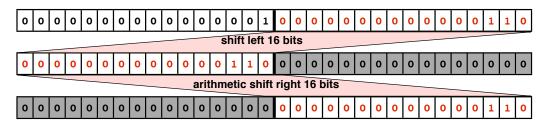

| 3.13                                                                                                                                                                      | Force high halfword to contain only low halfword sign bit 60                                                                                                                                                                                                                                                                                                                |

| 3.14                                                                                                                                                                      | Loop templates                                                                                                                                                                                                                                                                                                                                                              |

| 3.15                                                                                                                                                                      | if templates                                                                                                                                                                                                                                                                                                                                                                |

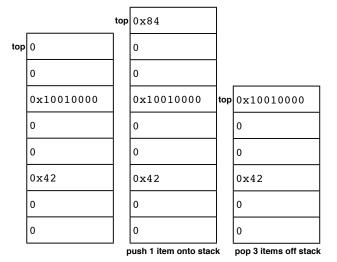

| 4.1                                                                                                                                                                       | Abstract stack example                                                                                                                                                                                                                                                                                                                                                      |

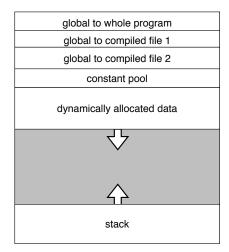

| 4.2                                                                                                                                                                       | Conceptual memory layout                                                                                                                                                                                                                                                                                                                                                    |

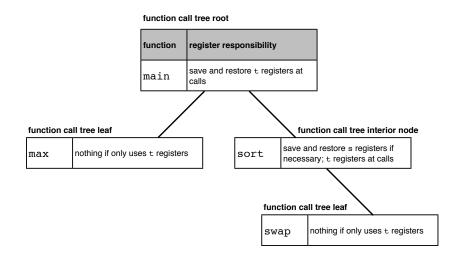

| 4.3                                                                                                                                                                       | Function call tree and register saving                                                                                                                                                                                                                                                                                                                                      |

| 4.4                                                                                                                                                                       | Saving the return address                                                                                                                                                                                                                                                                                                                                                   |

| 4.5                                                                                                                                                                       | More general loop and <b>if</b> templates                                                                                                                                                                                                                                                                                                                                   |

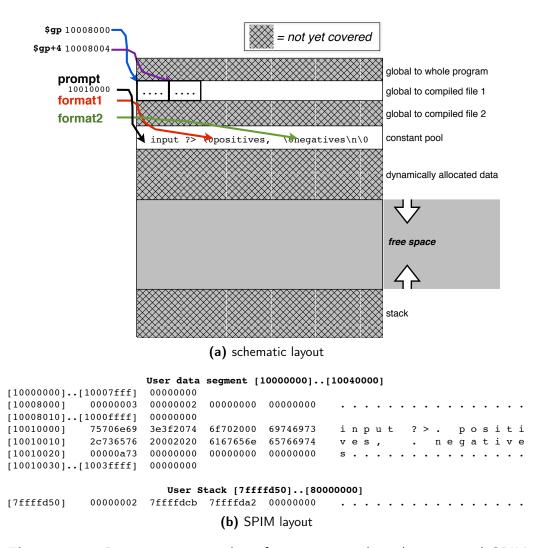

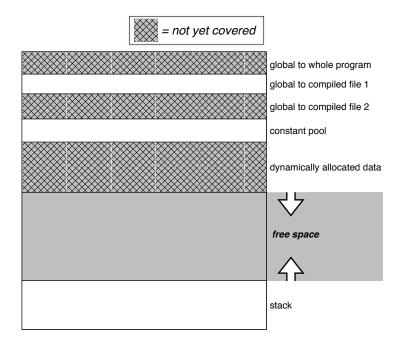

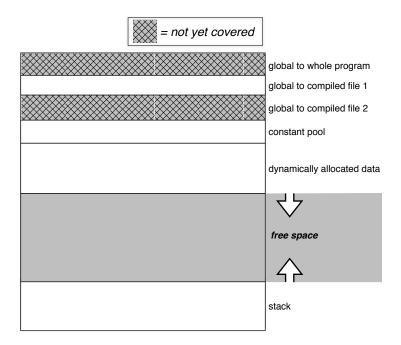

| 4.6                                                                                                                                                                       | Data segment used so far                                                                                                                                                                                                                                                                                                                                                    |

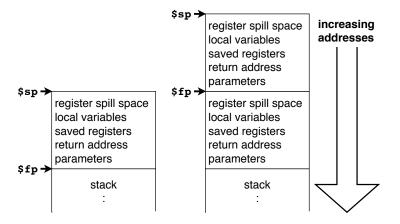

| 4.7                                                                                                                                                                       | More detail of stack storage scheme                                                                                                                                                                                                                                                                                                                                         |

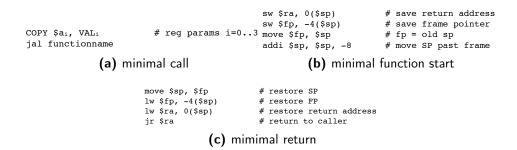

| 4.8                                                                                                                                                                       | Minimal function call templates                                                                                                                                                                                                                                                                                                                                             |

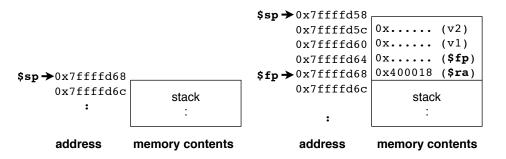

| 4.9                                                                                                                                                                       | Stack frame: minimal example with two words for variables 10                                                                                                                                                                                                                                                                                                                |

| 4.10                                                                                                                                                                      | More general function templates                                                                                                                                                                                                                                                                                                                                             |

| 4.11                                                                                                                                                                      | Data segment used so far (stack)                                                                                                                                                                                                                                                                                                                                            |

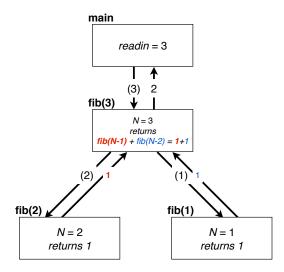

| 4.12                                                                                                                                                                      | Call tree for running a Fibonacci example                                                                                                                                                                                                                                                                                                                                   |

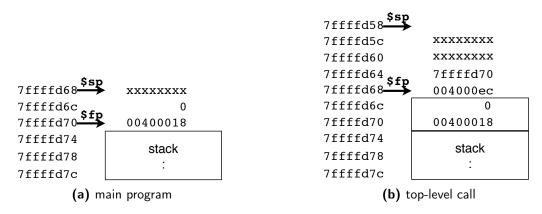

| 4.13                                                                                                                                                                      | Stack frame at two stages of the Fibonacci program                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                             |

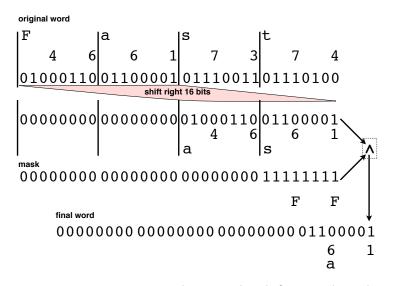

| 5.1                                                                                                                                                                       | Extracting a character by shifting and masking                                                                                                                                                                                                                                                                                                                              |

| 5.1<br>5.2                                                                                                                                                                | Extracting a character by shifting and masking                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                             |

| 5.2                                                                                                                                                                       | Indexing elements of 4 bytes                                                                                                                                                                                                                                                                                                                                                |

| 5.2<br>5.3                                                                                                                                                                | Indexing elements of 4 bytes                                                                                                                                                                                                                                                                                                                                                |

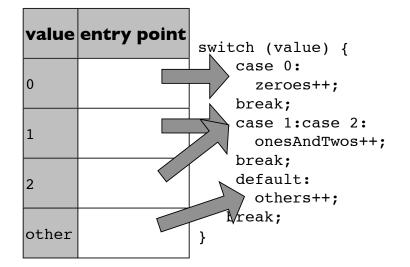

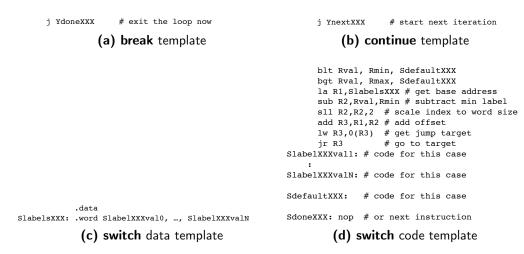

| 5.2<br>5.3<br>5.4                                                                                                                                                         | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue138                                                                                                                                                                                                                                                                  |

| 5.2<br>5.3<br>5.4<br>5.5                                                                                                                                                  | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue139Switch as seen in SPIM14                                                                                                                                                                                                                                          |

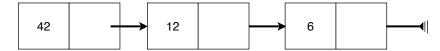

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6                                                                                                                                           | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue138Switch as seen in SPIM144Linked list144Minimal malloc implementation144                                                                                                                                                                                           |

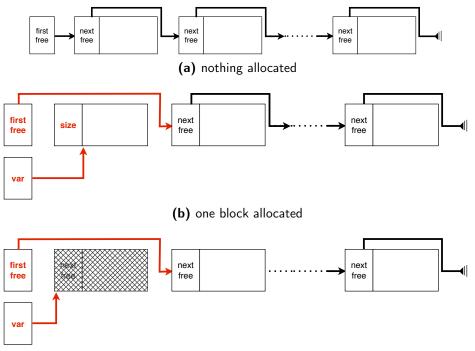

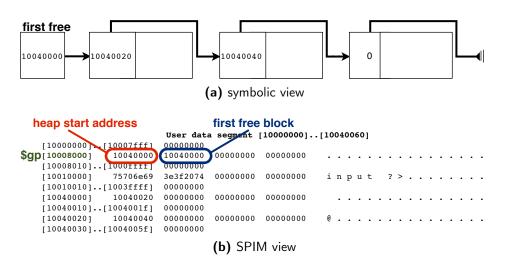

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7                                                                                                                                    | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue139Switch as seen in SPIM144Linked list144Minimal malloc implementation144Before and after SBRK144                                                                                                                                                                   |

| <ol> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> </ol>                                                        | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue139Switch as seen in SPIM144Linked list144Minimal malloc implementation144Before and after SBRK144Initialized heap: nothing allocated144                                                                                                                             |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10                                                                                                              | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue139Switch as seen in SPIM144Linked list144Minimal malloc implementation144Before and after SBRK144                                                                                                                                                                   |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                                                                      | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue138Switch as seen in SPIM144Linked list144Minimal malloc implementation144Before and after SBRK144Initialized heap: nothing allocated144Simple list example154                                                                                                       |

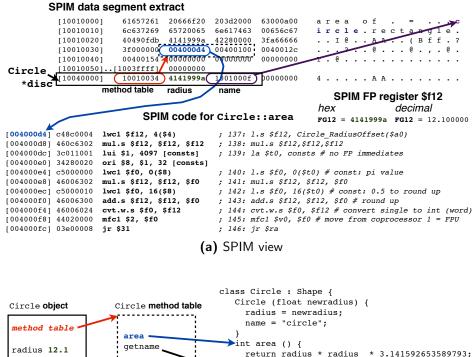

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11                                                                                                      | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue139Switch as seen in SPIM144Linked list144Minimal malloc implementation144Before and after SBRK144Initialized heap: nothing allocated144Simple list example154Implementation of an object164                                                                         |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12                                                                                              | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue139Switch as seen in SPIM144Linked list144Minimal malloc implementation144Before and after SBRK144Initialized heap: nothing allocated144Simple list example154Implementation of an object164Data segment used so far (stack)164                                      |

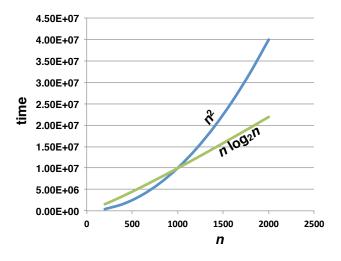

| <ul> <li>5.2</li> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> <li>5.10</li> <li>5.11</li> <li>5.12</li> <li>6.1</li> </ul> | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue139Switch as seen in SPIM144Linked list144Minimal malloc implementation144Before and after SBRK144Initialized heap: nothing allocated144Simple list example154Implementation of an object164Data segment used so far (stack)17                                       |

| 5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>6.1<br>6.2                                                                                | Indexing elements of 4 bytes134Conceptual view of a switch138More templates: switch, break and continue139Switch as seen in SPIM144Linked list144Minimal malloc implementation144Before and after SBRK144Initialized heap: nothing allocated144Simple list example154Implementation of an object164Data segment used so far (stack)164The benefits of a better algorithm174 |

### LIST OF FIGURES

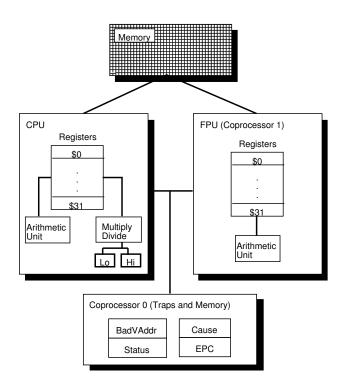

| E.1 | MIPS R2000 CPU and FPU                                              | 208 |

|-----|---------------------------------------------------------------------|-----|

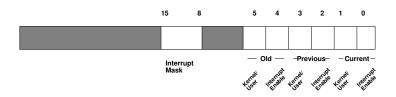

| E.2 | The Status register.                                                | 210 |

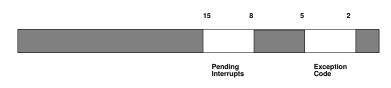

| E.3 | The Cause register                                                  | 210 |

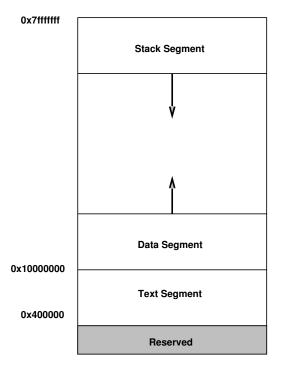

| E.4 | Layout of memory.                                                   | 221 |

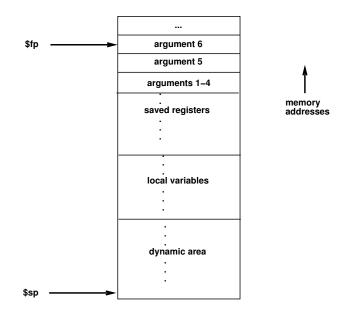

| E.5 | Layout of a stack frame. The frame pointer points just below the    |     |

|     | last argument passed on the stack. The stack pointer points to the  |     |

|     | last word in the frame.                                             | 222 |

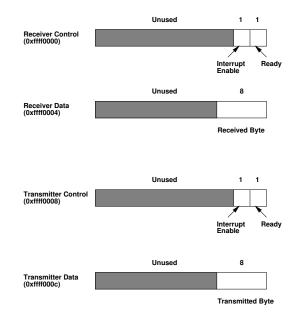

| E.6 | The terminal is controlled by four device registers, each of which  |     |

|     | appears as a special memory location at the given address. Only a   |     |

|     | few bits of the registers are actually used: the others always read |     |

|     | as zeroes and are ignored on writes.                                | 224 |

|     |                                                                     |     |

viii

# **List of Tables**

| 1.1 | ASCII encoding example                                    |

|-----|-----------------------------------------------------------|

| 1.2 | Binary and Decimal Units                                  |

| 2.1 | Nand truth table                                          |

| 2.2 | And and Or truth table                                    |

| 2.3 | De Morgan's Law truth table                               |

| 2.4 | And, Or, Xor truth table                                  |

| 2.5 | 2's complement examples                                   |

| 2.6 | Half adder truth table                                    |

| 2.7 | Full adder truth table                                    |

| 2.8 | Register conventions                                      |

| 5.1 | Sizes of standard C basic types                           |

| A.1 | ASCII encoding                                            |

| A.2 | ASCII non-printing character encoding                     |

| B.1 | Register conventions including floating point             |

| C.1 | SPIM system calls                                         |

| E.1 | System services                                           |

| E.2 | MIPS registers and the convention governing their use 209 |

# Definitions

A

absolute address - Address that can be used directly. See also address, relative address.

*absolute path* – A path from the root of the file system, in UNIX designated by starting with "/". See also *system path*, *relative path*, *path*.

abstraction - The principle of hiding all but the most essential details.

activation record – See stack frame.

actual parameter - See parameter.

*address* – Number signifying position relative to the start of main memory (RAM); usually numbered in bytes. See also *absolute address, relative address, pointer*.

ALU – See arithmetic-logic unit.

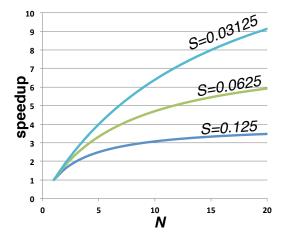

Amdahl's Law – A version of the speedup formula that emphasises the sequential fraction.

architecture – A consistent design that allows a range of implementations, each running the same code subject only to available resources (memory, speed, connected devices). The Intel IA32 architecture for example runs the same 32-bit instruction set across many designs going back to the 80386, also called Intel386, i386, or 386, going back to 1985.

argument - See parameter: term used in C-family languages for the value passed in.

arithmetic-logic unit (ALU) - component of CPU that decodes and executes instructions.

*array* – Data structure: elements accessed by (usually) integer index; in C, all elements are the same type and an array is represented by the *address* of (*pointer* to) the first element.

- ASCII American Standard Code for Information Interchange a 7-bit, extended to 8 bits, code for representing characters. See also Appendix A.

- assembler A program that translates assembly language to machine code. See also assembly language.

- assembler directive An instruction to an assembler that does not generate code. See also assembler.

- *assembly language* A symbolic representation of machine code that mostly translates directly to machine code instructions. See also *assembler*, *pseudoinstruction*, *assembler directive*.

- bias A way of representing positives and negatives where a bias has to be subtracted from the number to represent its true value. In IEEE floating point, the exponent is represented this way (bias = 127). Also called *offset* or *excess*.

- *big endian* Ordering of smaller items like bytes within a word that starts at the high-order (big) end of the word, so bytes within a word appear in memory in order 0,1,2,3. See also *little endian, endianness*.

B

*bit* – Binary digit (0 or 1 in a number represented in base 2).

boolean algebra – Rules for arithmetic with true (1) and false (0) values.

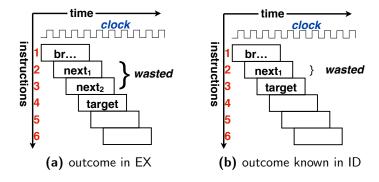

- *branch delay slot* The instruction immediately after a branch that is executed whether the branch is taken or not. See also *delayed branch*.

- *branch instruction* Changes flow of control conditionally; encodes a condition and also has a *target address*. A branch is *taken* if the condition is true. The address is usually *relative*. See also *jump* instruction, *delayed branch*.

- *bytecode* A machine instruction set designed to be *portable*, usually interpreted or translated to actual machine code.

С

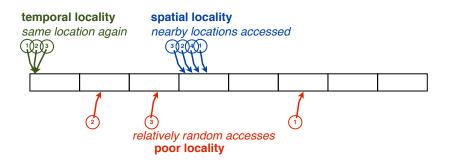

*cache* – A fast memory that is used to fake the effect of the entire memory being faster than a reasonably affordable memory technology. Decisions as to what is in a faster layer are made in hardware. The fastest cache is integrated into the *CPU* in recent designs, and is the *highest-level* or *level 1* (also: *L1* cache). There can be 1 or more lower levels of cache, usually in current designs integrated into the *CPU* chip, numbered L2, ...

*CISC* – See *complex instruction set computer*.

- *compiled* Translated with significant changes in amount and style of code from a *high-level language* to a lower-level language (usually *machine code*.

- complement In logic, inversion of all bits. See also two's complement.

- *complex instruction set computer (CISC)* Any design that does not fit the *RISC* definition. For example, with variable instruction lengths, instructions that only work with specific registers and instructions that do arithmetic or logic on memory contents.

- *complexity* Growth rate of time or extra space needed by an algorithm expressed as the largest term of a function of size of data *N*. See also *space complexity, time complexity, complexity class*.

- *complexity class* Classification of a function in terms of its growth rate based on the largest term. See also *complexity*.

- constant pool Region of memory containing constant values such as strings. See also heap, stack, globals.

- *conditional* A C *operator* that given a boolean value selects between two alternatives. Written bool ? alt<sub>1</sub> : alt<sub>2</sub>.

- *contradiction* In logic, any formula that is **false** for all values of variables (or in a logic circuit, all inputs). See also *tautology*.

- *coprocessor* An auxiliary processor outside the main logic path. See also *floating-point unit*, *graphics processing unit*.

- *core* In designs with multiple *CPUs* on a chip (*multicore*), each *CPU* is called a core. Cores often share the lowest-level on-chip *cache*.

*CPU* – See *processor*.

D

- *declaration* In C, the place where the type of a program construct (function, type or variable) is known but does not require runtime resources. See also *definition*.

- *definition* In C, the place where a program construct (function or variable) requires runtime resources. See also *declaration*.

- *delayed branch* A branch instruction that executes the following instruction whether the branch is taken or not. See also *branch delay slot*.

- De Morgan's Laws In logic, rules to redistribute negation over and and or.

- *digit signal processor (DSP)* A specialized *CPU* that is designed for efficient digit-analog conversion as in audio or video.

- *dispatch table* Table of addresses that can be used in a jump or similar instruction to direct to code based on an index. See also *jump table*.

- DRAM See dynamic random access memory.

- DSP See digit signal processor.

- *dynamic instruction count* Count of instructions executed in a particular run of a program. See also *static instruction count*.

- *dynamic linking* Linking that is delayed until a program runs. See also *linker*, *library*, *static linking*, *executable file*, *object file*.

- *dynamic random access memory (DRAM)* RAM usually implemented with a capacitor storing a bit that needs to be refreshed periodically to maintain its value: relatively inexpensive, but not as fast as *SRAM*.

#### Е

embedded system – A computer that is part of another machine or device.

endianness – Intel architectures are little-endian; MIPS can be either. See also little endian, big endian.

excess – See bias.

executable file - A file that can be run directly. See also linker, object file.

#### F

- floating point Computer representation of numbers that can include fractions. Most *CPUs* that support floating point have a separate set of registers for floating point values. The IEEE 754 standard defines a range of different sizes of floating-point numbers and includes concepts like representing  $\pm \infty$  and not a number (or NaN).

- *floating-point unit (FPU)* Component of a *CPU* that handles floating-point instructions, usually with its own register set. See also *coprocessor*.

- formal parameter See parameter.

- FPU See floating-point unit.

- *frame pointer* Register to keep track of the start of the current *stack frame*. MIPS machine code convention: register 30 (\$fp or \$30). Some compilers do not use a frame pointer (if you know the size of the stack frame, you can work out everything you need from the *stack pointer*).

- *function (procedure, subroutine)* Unit of code that can be invoked with a return address to return to the point immediately after invocation; optionally can include parameters passed in, local variables and a return value. In object-oriented languages, a *method* is the same thing with added features: the ability to reference a specific object, and the possibility of finding a different version of the method by inheritance.

#### G

- *garbage collector* Recovers memory no longer accessible by a program, usually when memory starts to fill up. See also *heap*, *managed-memory language* not a feature of C.

- gate Elementary logic function implemented in hardware. See universal gate.

general-purpose computing on graphics processing units (GPGPU) – Using a GPU to speed up non-graphics computation.

GPGPU – See general-purpose computing on graphics processing units.

GPU – See graphics processing unit.

graphics processing unit (GPU) – Component of a CPU that handles graphics instructions, sometimes on a separate chip. See also coprocessor.

H

- *hard real time* A real-time requirement that if not met means system failure. See also *real time*, *soft real time*.

- *heap* Region of memory containing dynamically allocated and deallocated data (also the name of a data structure). See also *globals*, *stack*, *constant pool*.

- *hexadecimal (hex)* Base 16 convenient for representing binary numbers since grouping bits in 4s starting from the low end of the number converts directly to hex.

- *high-level language (HLL)* A language designed for human convenience of programming, not close to the machine. See also *assembly language*.

- *HLL architecture* Machine instruction set designed to be closer to a *high-level language* than traditional *machine code*.

I

*IEEE 754* – See *floating point*.

*ILP* – See *instruction-level parallelism*.

immediate operand - An operand value encoded into the instruction. See also operand.

- *infix notation* Function names are written between *operands*, as in arithmetic expressions. See also *postfix notation*.

- *inheritance* Ability in object-oriented languages to derive a new class from a parent class with the option to reuse or override methods of the parent class not a feature of C (can be built up laboriously in machine code).

instruction count – See static instruction count, dynamic instruction count.

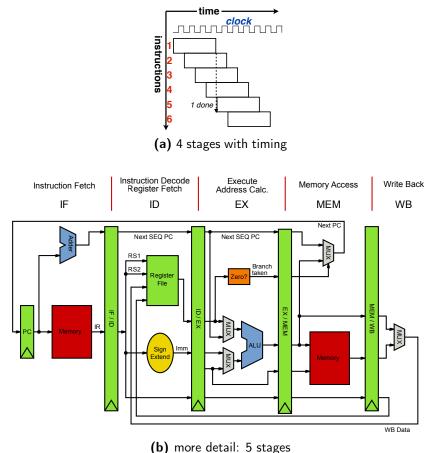

- *instruction issue* Transition of an instruction to the execute stage (or first execute stage, with a deeper pipeline).

- *instruction-level parallelism (ILP)* Increasing *CPU* throughput by overlapping execution of instructions.

instruction set architecture (ISA) – Instruction set as seen by the programmer or compiler.

interpreted – Executed line-by-line, as opposed to compiled.

*interrupt* – Event that breaks the sequence of execution, often resulting in use of a jump table to find an interrupt handler. See also *interrupt handler*, *interrupt vector*, *jump table*.

- *interrupt handler* Code invoked to handle an *interrupt*. Generally must be short to minimise backing up other interrupts.

- *interrupt vector* Sequential (possibly with gaps) locations to which control transfers on an *interrupt*, with one location for each type of interrupt.

- *ISA* See *instruction set architecture*.

- *issue* See *instruction issue*.

### DEFINITIONS

#### JIT – see just in time compiler.

- *jump instruction* Changes flow of control unconditionally; a *jump and link* instruction stores the *return address*. The address may be *immediate* or from a *register* but is usually *absolute*. See also *branch* instruction.

- *jump table* Table of jump instructions that can be used to transfer control code based on an index. See also *interrupt*, *dispatch table*.

- *just in time (JIT) compiler* A *compiler* that translates to machine code immediately before the particular code is needed; sometimes used as an alternative to interpreting *bytecode*.

L

- L1, L2, etc. First, second, etc., levels e.g. of a *cache* hierarchy in which L1 is the fastest and closest to the *CPU*.

- label A name used in assembly language to mark a location in memory (an instruction or a location where a constant has been placed; in SPIM's assembly language, a label has a ":" after its name where it is defined.

- *library* Precompiled code available to link into programs. See also *linker*, *dynamic linking*, *static linking*.

- linker A program that combines separately compiled files. See also object file, library.

- *little endian* Ordering of smaller items like bytes within a word that starts at the low-order (little) end of the word, so bytes within a word appear in memory in order 3,2,1,0. See also *big endian, endianness*.

- load An instruction that copies memory contents to a register (in MIPS, there are different load instructions for different sizes and types of operand, e.g., lw loads a word into an integer register). See also *store*.

- *locality* The principle that a program uses a small subset of memory at a time. See also *spatial locality*, *temporal locality*.

#### Μ

- *machine code* Instructions that are directly *interpreted* by hardware with no further translation. See also *assembly language*.

- *macro* Named text that can be substituted into other text by use of its name. Macros can also have parameters; distinguished from *functions* in that they have no clear existence at run time.

- *make* A UNIX utility that uses a Makefile (capital "M" optional) containing dependence rules and actions to resolve failed dependences.

- *managed-memory language* A language in which inaccessible dynamically allocated data space is automatically. See also *garbage collector*.

- *memory leak* A program not written in a *managed-memory language* starts to run out of memory because the program does not correctly deallocate dynamic data when it is no longer accessible.

- *method* not a feature of C or machine code (directly you can make up a similar concept with some effort) see *function*.

MIPS - A RISC processor architecture common in embedded devices.

*multicore* – See *core*.

Ν

*null pointer* – A pointer value that represents no memory location, usually a zero. See also *pointer*. **O**

- *object file* A compiled portion of a program that must be combined with other files to make an executable file. See also *linker*.

- *one's complement (1's complement)* A way of representing integer negatives, by inverting all bits. Not widely used since unlike *two's complement*, it has a wasted value with zero represented two ways, as all 0s or all 1s.

- offset See bias.

- *opcode* Part of an instruction that signifies what operation it performs (in MIPS, modified by *function* bits).

- *operand* In a MIPS instruction or C expression, value to be used or in MIPS a destination for computed value. See also *immediate operand*, *register*, *infix notation*.

- operator A built-in function with a special symbol, usually in *infix* notation, such as + or \*.

Р

- *parameter* value passed in to a function. In the function definition, called a *formal parameter* and in the call, an *actual parameter*. In C, a formal parameter is called a *parameter*, and an actual parameter an *argument*.

- *path* Sequence of directory names, in UNIX separated by "/". See also system path, relative path, absolute path.

- pipeline Organization of instruction execution overlapping sequential instructions. See also stall.

- pointer A value that contains a memory address. See also null pointer, reference.

- *pop* Remove an item from the top of a stack, adjusting the stack pointer back an item. See also *stack*, *push*.

- portable Designed to run on more than one machine, possibly very different machines.

- *postfix notation* Function names are written after an *operand*, as in arithmetic expressions. See also *infix notation*.

- procedure See function: a name used in older languages including Pascal.

- processor Logic unit that interprets instructions and includes the fastest layers of memory, registers and caches. Also called *central processing unit (CPU)*. See also *core*, *arithmetic-logic unit*.

- program counter (PC) Register to keep track of the current instruction being executed. On MIPS, it always is a multiple of 4 since instructions are word-aligned. Advances by 4 each instruction, unless a flow control instruction changes it (jump or branch).

- *pseudoinstruction* An instruction in assembly language that is not a real machine instruction but translates to one or more real machine instructions. See also *assembler*.

- push Add an item onto the top of a stack, advancing the stack pointer. See also stack, pop.

### R

RAM – See random access memory.

*random access memory (RAM)* – Any memory that has an addressing scheme that equally allows any item to be accesses without e.g., a delay to make that region accessible.

*real time* – A requirement that a task be done by a time deadline. See also *hard real time*, *soft real time*.

recursion - See recursion.

- reduced instruction set computer (RISC) An architecture in which all memory accesses are via loads (copy to a register) or stores (copy a register to memory), all arithmetic and logic is through registers, and instructions have relatively simple formats without variations in instruction length. Also has a large set of general-purpose registers (MIPS has 32 integer registers, though register zero -\$zero or \$0 – is hardwired to zeroes and register 31 – \$ra or \$31 – is hardwired as the return address register). See also CISC.

- reference Slightly disguised *pointer* in languages with a higher-level approach than C.

- *register* Extra-fast memory designed into the *CPU* logic; usually a very limited number. Register addresses are usually hard-coded into instructions for speed. See also *spill registers*, *frame pointer*, *stack pointer*, *program counter*, *reduced instruction set computer*.

- *relative address* Address that must be added to a given location (usually the PC). See also *address, absolute address.*

- *relative path* Path in UNIX starting with anything but "/", relative to the current working directory. See also *system path, path, absolute path, working directory.*

- *return address* Usually the address of the next instruction after a call instruction (e.g., jump and link, jal). The MIPS architecture stores the return address in register 31 (\$ra or \$31, but you can overrule this with the jalr instruction, which encodes a return address register).

*RISC* – See *reduced instruction set computer*.

S

- *shell* In UNIX-like systems, the environment where you run programs including a scripting language.

- *short-circuit evaluation* Evaluation usually of logical or boolean expressions that stops as soon as the answer is known.

- sign bit A bit used to signify negative (usually 1) or positive (usually 0). See also two's complement and signed magnitude.

- signed magnitude A way of representing integer negatives, by using the same bit representation for a negative and positive, except the sign bit is 1 for a negative. Used in IEEE floating point. See also two's complement.

- *spatial locality* The principle that a program tends to use memory close to each other. See also *locality, temporal locality.*

- *soft real time* A real-time requirement that if not met can be handled by a fallback option like a drop in quality. See also *real time*, *hard real time*.

- *space complexity Complexity* expressed in terms of extra space needed by an algorithm over and above the initial data. See also *time complexity, complexity class*.

- speedup After a change,  $\frac{t_{before}}{t_{after}}$ . See also Amdahl's Law.

- spill registers Save registers to RAM, usually on a function call.

- SRAM See static random access memory.

- stack At hardware level, a region of memory used to represent the state of function calls including local variables, values that have to be saved across calls, parameters and the return address. See also push, pop, heap, globals, constant pool, spill registers.

- *stack frame (activation record)* Contents of the stack representing the state of one particular function call.

- *stack pointer* Register to keep track of the top of the stack. In MIPS machine code, by convention, this is register 29 (\$sp or \$29). See also *frame pointer*.

static definition – In C: function or variable with a name only visible in one compiled source file.

- *static instruction count* Count of the number of instructions in a program. See also *dynamic instruction count*.

- *static linking* Linking that is done when creating an executable file. See also *linker*, *library*, *dynamic linking*, *executable file*, *object file*.

- *stall* One or more lost cycles when a pipeline is unable to continue.

- static random access memory (SRAM) RAM usually implemented with a transistor storing a bit that does not need to be refreshed periodically to maintain its value: relatively expensive, and is faster than DRAM. Also requires more components than DRAM per bit, and hence not as dense, which is why it is more expensive. Generally used for caches.

- store An instruction that copies register contents to memory (in MIPS, there are different store instructions for different sizes and types of operand, e.g., sw stores a word from an integer register). See also *load*.

- structured data A data type composed of one or more elements, not necessarily of the same type. Called a struct in C; a class is the same concept but with *methods* and *inheritance* added. subroutine – See function: a name used in older languages including FORTRAN.

- *system path* Sequence of path names, in UNIX separated by ":" used to find executables run with no path name. See also *path*, *relative path*, *absolute path*.

Т

- *taken branch* When the branch condition is true and the branch instruction jumps to the target address rather than falling through to the next instruction, the branch is taken. See also *branch*.

- *tautology* In logic, any formula that is **true** for all values of variables (or in a logic circuit, all inputs). See also *contradiction*.

- *temporal locality* The principle that a program is likely to use the same memory again some time soon. See also *spatial locality*, *locality*.

- *time complexity Complexity* expressed in terms of run time of an algorithm. See also *space complexity, complexity class.*

- *truth table* Table showing all possible values of a logical or boolean function, given all possible inputs.

- two's complement (2's complement) A way of representing integer negatives, by inverting all bits and adding 1. In 2's complement arithmetic, an overflow occurs if there is a carry in or out of the sign bit, but not both. See also one's complement.

U

universal gate - A gate that can be used to implement all other logic functions.

#### W

- *word-aligned* On a byte-addressed machine, an address that is an even multiple of the word size (in MIPS, a multiple of 4).

- *working directory* Directory relative to which paths are defined. See also *path*, *relative path*, *absolute path*.

Z

\$zero - See reduced instruction set computer.

DEFINITIONS

xviii

# **1** Introduction

**P**ROGRAMMING IN MANAGED-MEMORY LANGUAGES like Java, Python and C# takes a lot of pain out of programming, but also takes away the need to *understand* at a deep level what is going on. Often, that is good enough. You just want to get the job done with minimum pain, and with minimal chance of programmer error.

By "managed-memory language", I mean one where you do not have to deallocate memory explicitly. Such languages also often include large libraries of carefully-worked-out data structures and algorithms, so you don't have to code these rather basic things from scratch.

Why, anyway, would anyone want to get rid of such conveniences as automatic memory management, high-level abstractions of data structures and classes with inheritance? There are times when extreme efficiency is a concern, such as programming a very small device, or where a task has to finish within a predicted time.

How real are these scenarios?

# Embedded

Don't most computers you buy today have multiple cores running at over 2GHz and RAM measured in Gbytes? Wrong. Most computers sold today are very small devices that are part of another machine. There are obvious ones like MP3 players, that you would know are in essence a scaled-down computer, and slightly less obvious ones like a home ADSL router. But small computers are part of many other things in less obvious ways – washing machines, cars, smaller home appliances – to quote a few examples. When a computer is part of another machine, it is called an *embedded system* and embedded systems may have severe cost and power-use constraints. What's more, they may have to continue running unattended for years in the field, so they need to be simple and robust – and not

run out of memory or processing speed because of minor efficiency issues.

# **Real Time**

What of systems where time to complete is critical? A real-time system is one where specific tasks have hard time limits. A *hard read-time* task is one where failure to complete in time means the system is broken. Think anti-lock brakes on a car. If the computer controlling the anti-lock system doesn't react in time, the system is flawed. A *soft real-time* task is one where there is an acceptable failure mode if you run out of time. Think digital TV that pixellates when the signal is lost – quality suffers but to a point you can tolerate that sort of failure.

While real-time and embedded systems can be programmed with managedmemory languages, there are times when efficiency and timing predictability are important enough to justify a language close to the hardware so you know exactly what is going on without a few layers hiding *how* things work from the programmer.

# Why

Those examples are a partial justification. In addition, for someone studying Computer Science (or related subjects), a deeper understanding is called for. You need to know what is going on under the hood, just as a mechanical engineer who wants to design cars needs to understand how they work, not just how to drive them (or plug in an automated diagnostic tool).

Abstraction is an important design issue both in programming language design and in programming – hiding the *how* and allowing the programmer to focus on the *why*. Nonetheless, someone has to know what is going on underneath, otherwise we cannot create new programming languages and tools like compilers.

So, in this book, we take a break from the world of managed-memory languages and high-level abstractions, and start from the bottom up to see how things work. By the end of the first part, you should have a good idea of how a lowlevel language like C is implemented, and some idea of how higher-level concepts like objects map to the hardware. The second part switches to C programming to build on your understanding of the low-level concepts.

The aim is to give you base from which you can move in any direction, from learning more about hardware to using higher-level languages with a clearer understanding of how they work.

To help you see the big picture, every now and then you will see a grey box. These are of two types to emphasise different kinds of important points.

The first is a "takehome", as illustrated here:

**The take home message?** Sometimes it is useful to focus on one point to understand the purpose of a particular section.

The second is a "headsup", of which an example follows:

**Heads up:** Sometimes you need to know that a particular point or issue could cause confusion, so you need to pay particular attention to it.

# **1.1 Some Basics**

At its lowest level, a computer is an electronic device that responds to different voltage levels you can think of as representing 0s and 1s. These binary digits or *bits* each represent one of two values but in combination represent as wide a range of values as we need. Because a 0 can be thought of as a logical **false** value and a 1 as a logical **true** value, we can build up complicated operations by combinations of simple boolean logic. Everything stored in a computer is represented as bits; the actual interpretation of a given string of bits depends on the program. An instruction at the machine level is just a string of bits; the same sequences of 0s and 1s could represent a location in memory, an integer value, a floating-point value or a sequence of characters.

If you program in a managed-memory language, this very basic feature of a computer is hidden – you don't get to see how, for example, locations in memory are represented, or manipulate them. You may have a high-level construct like a *reference* that allows you to store the location of an object in a variable, but you probably cannot do something like add 4 to the reference to make it point to another part of memory, or reinterpret the bit string representing the reference as another type of data.

Why would you want to do things like this?

If you are writing a compiler, one of the things you need to do is create machine-level instructions. A machine-level instruction, as we will see, includes components that are a fixed bit pattern, and may include other components representing data values or locations in memory. To create a machine instruction,

| char | encoding |   |   |   |   |   |   |

|------|----------|---|---|---|---|---|---|

| %    | 0        | 1 | 0 | 0 | 1 | 0 | 1 |

Table 1.1: ASCII encoding example: the per cent symbol

you need to be free to switch what a given bit pattern represents at one point (for example, an integer) to something else containing the same bits (a segment of a machine instruction). Here, we are not going to look at machine instructions as bit patterns too often: we use a slightly more convenient notation called *assembly language* that can be translated relatively straightforwardly to machine code by a program called an *assembler*.

Let's look at some examples.

Characters at machine level can be represented in various ways. A simple approach is to use 8 bits to represent characters, as in ASCII (American Standard Code for Information Interchange). A more modern design, Unicode, uses 16 bits, sufficient to represent more complex alphabets. For our examples, to keep things simple, we'll stick with ASCII. ASCII was originally designed as a 7-bit code, and the first 32 codes (numbered 0–31) are *non-printing* characters designed for purposes like controlling printers or inserting codes in a data stream (such as an end of file marker). ASCII evolved to an 8-bit code with several variants allowing for extensions like accented characters in languages that use them. We will stick to the simple alphanumeric subset of ASCII, including punctuation and control characters – the original 7-bit design.

Here is an example. The character "%" is encoded as the number 37, or the bit pattern in table 1.1. This bit pattern represents the binary number  $100101_2$ . There is a full listing of printable ASCII characters and a partial list of the more interesting non-printing characters in Appendix A.

Already, we have seen that this one bit pattern can represent two completely different things. In the MIPS instruction set (of which more later), 6 bits are used to signify operations. The same 6 bits that represent the "%" character (not counting the 0 at the high end of the number) as a MIPS operation signifies a logical **or** between two registers.

**The take home message?** A bit pattern can represent many things, and the context and how it is used determines what it actually means.

# **1.2** Machine Language versus High-Level Language

How different are the low-level machine instructions from a language you may be familiar with?

To start with, I will use a made up assembly language to express machine instructions to give you a taste of what they look like; we will later graduate to using the MIPS instruction set, which is only a little more difficult. I will express programs in a pseudocode similar to C and translate them to assembly language. We will later use a systematic approach for this, to get a feel for how a compiler would do it.

Let's take a simple construct – a **for** loop that adds the first N numbers from 0 up. Here it is in my C-like pseudocode:

```

sum = 0;

for (i = 0; i < N; i++)

sum += i;

```

**Heads up:** You may notice that my "pseudocode" looks suspiciously like a real programming language rather than an approximate design notation. This is deliberate: we will do C properly later so we might as well get used to how it looks. A real pseudocode notation of course does not follow syntax rules of a programming language and is allowed to leave out inessential details.

An instruction in general is divided into an *operation*, encoded in an *opcode*, and *operands* representing the data or machine address to be operated on. Our machine language has special fast memory locations called *registers* that we use to hold data values we are currently working with. Let's call these R0...R16, and assume that R0 always contains the value zero. Our machine has operations like test a value against a register for less than, and jump to a location if the test is true (a *branch* instruction, written as **brlt Ra,Rb,target**, meaning go to **target** if **Ra** < **Rb** – also sometimes called a *conditional branch*). We also assume a **brge Ra,Rb,target** instruction that tests for **Ra** ≥ **Rb**. We also can jump unconditionally to a location in our code (a *jump* instruction, written as **j target**). We can also do arithmetic between a pair of registers and store the result in a destination register. Finally, we can add comments to our code using a "#" symbol (the rest of the line after that is purely for the human reader). Our machine code looks something like this:

```

# assume N is in R1, use R2 to hold sum

# use R3 to store the loop counter i

add R2,R0,R0

\# sum = 0;

add R3,R0,R0

# for (i = 0; i < N; i++)

test: brge R3,R1,done

# test before first iteration

add R2,R2,R3

sum += i:

#

addi R3,R3,1

# increment loop counter

j test

# back to the test

done: nop

```

A few more details: note the **addi** instruction. This has an example of an *immediate* operand – a value built directly into the instruction, rather than fetched from elsewhere. In this case, the immediate value is a 1. Also note the **nop** (no-operation) instruction at the end of the loop. This is to provide a place to branch to – usually, there would be an actual instruction there that did something useful. Also note the use of *labels* – a word followed by a ":" in the left hand margin.

There is a fair amount of variation in notation in assemblers, aside from the fact that the actual instruction set differs from machine to machine. Some, for example, use a ";" symbol to mark comments. Another variation is using a "#" symbol to mark an immediate operand (obviously not so useful if the same symbol is used to start a comment), or a "\$" symbol at the start of a register name. When we look at how to program a MIPS machine we will see a few of these variants. If you use a specific assembler, you need to learn its conventions – but the main thing you need to learn if you switch to a different machine is how its instruction set differs.

**Heads up:** The MIPS assembler we use uses the "#" comment convention but when displaying programs at run time in the debugger, uses a ";" as a comment separator to keep things interesting.

Here is another variation. If we do the test at the end of the loop, our code saves one instruction execution every time it goes through the loop body, at the cost of a wasted jump instruction at the top. Also, if we branch from the test at the end of the loop, we can eliminate the need to the extra **nop** instruction:

# assume N is in R1, use R2 to hold sum

# use R3 to store the loop counter i

add R2,R0,R0 # sum = 0;

add R3,R0,R0 # for (i = 0; i < N; i++)</pre>

6

j test # test before first iteration body: add R2,R2,R3 # sum += i; addi R3,R3,1 # increment loop counter test: brlt R3,R1,body # not done? Go again

The number of instructions executed in a particular run of a program is called the *dynamic instruction count*. The number of instructions you count by reading the program is called the *static instruction count*. If you don't count the **nop** instruction, the two versions of the code have the same static instruction count (6 instructions). The dynamic instruction count, however, is lower since the repeated parts of the loop are shorter by 1 instruction. That may not look like a lot, but loops are where many programs spend most of their time, and shortening the loop dynamic instruction count by 25% per iteration (reducing from 4 to 3 instructions) is a significant improvement. Usually, if memory is not tight, you are prepared to make your code take up more memory (higher static instruction count – though there are other tricks like more efficient memory access that can reduce run time without reducing the number of instructions executed. For more on performance, see chapter 6).

The notation I use here for our machine instructions is of course rather different from the actual machine code on a real machine, which is just a string of 1s and 0s. Assuming we know how to encode instructions (which bits signify the operation, which signify the register names, and so on), it is mostly straightforward to convert our notation to machine code (if tedious and errorprone). We also need to convert the names "**test**" and "**done**" to a numeric representation in the instructions that use them. Hardly anyone actually programs directly in machine code because an assembler, a relatively simple program, can do this sort of conversion from a convenient notation for machine instructions, assembly language, to real machine instructions. Though assembly language rules are simple, an assembler can still throw out a program for violating the rules.

In our simple loop example, the conversion from C-like code to assembly language is quite straightforward. As we will see with MIPS machine code, the assembly language for which is not far from my made-up assembly language example, things get a lot more complicated when you deal with examples with more intricate logic or data structures. **The take home message?** An assembler provides a more convenient notation than machine code, though that notation is still very close to the machine and not at all similar to a programming language you may be used to.

### **1.3 Code Translation**

An assembler is a relatively simple program – mostly, there is a one-to-one mapping between lines of code and machine instructions. The assembler must keep track of names you use for labels, and needs to know how to create the bit pattern for every instruction. Some assemblers include *pseudoinstructions* – instructions that don't translate directly to machine code, but still can convert to at most one or a small number of instructions.

In my small example, I translate

sum = 0;

add R2,R0,R0

This is not the only way to zero a variable. You could also do a logical and with zero. However, to the human reader, an instruction that copies the zero register (R0) to another register is easier to understand. So an assembly may include a pseudoinstruction like

copy R2,R0

and this instruction actually translates as machine code for something like add R2,R0,R0. Since there is no real copy instruction, this is an example of a pseudoinstruction. The MIPS assembler we will be using has a number of pseudoinstructions. You do not need to know that they are not real machine instructions in most cases because the assembler takes care of translation to machine code. However, in a few cases, a pseudoinstruction translates to multiple machine code instructions, so it is useful to understand what is going on when you inspect the program in a debugger.

Converting to machine code where the gap between the language and machine is bigger is not so trivial. A language that is significantly different from the machine instruction set is called a *high-level language* (since "low-level" implies closer to the hardware). Languages with complex features that have no direct

### Code Translation

representation in the hardware like methods, objects, variable-sized arrays or lists require complex translation to machine code. The nearest we see to any of this is understanding how *function call* (also called procedure or subroutine call) works, and how to access data via a memory address. A function call is like a more primitive version of a method, in which you do not have the benefit of knowing the identify of the object that invoked the function (there are no objects at machine code level), or inheritance. Things like inheritance are of course layered on top of the machine by the language implementation. We get a sense of how that works in chapter 5.

There are two major approaches to translation to machine code. The first is *compiling*, where the original code is translated once to machine code, and the machine code (possibly with some additional work) can run directly on the machine. The second is *interpreting*, where the program is not converted to machine code but rather a program called an *interpreter* examines each program construct and decides what to do with it as the program runs.

Compilers are generally used for languages where it is hard to make sense of the code by looking at one line at a time. Interpreters tend to be used for simpler languages like scripting languages, where it is possible to make sense of the code without reading a lot of surrounding context.

An in-between case is a language that is translated to an intermediate form by a compiler, and that intermediate form (which is not machine code) is interpreted. An example is Java, which is compiled to an instruction set called *bytecode*, which can then be interpreted. Java is implemented this way for *portability*: any system that can interpret the bytecode program can run it. If a program is compiled to the real instruction set, it won't run directly on a different machine. Interpreting is generally slower than compiling so Java systems generally include a *just in time* or *JIT* compiler that converts bytecode to machine code the first time it's run.

At hardware level, machine code is run by an interpreter, but one implemented in hardware. Each instruction has to be loaded from RAM, analysed for the type of instruction, any data movements necessary set up and executed by the appropriate part of the CPU's logic.

**The take home message?** Compilers convert to machine code or something like it. Interpreters work with a program a small piece at a time but do not convert the program to machine code.

# **1.4 Machine Instruction Sets**