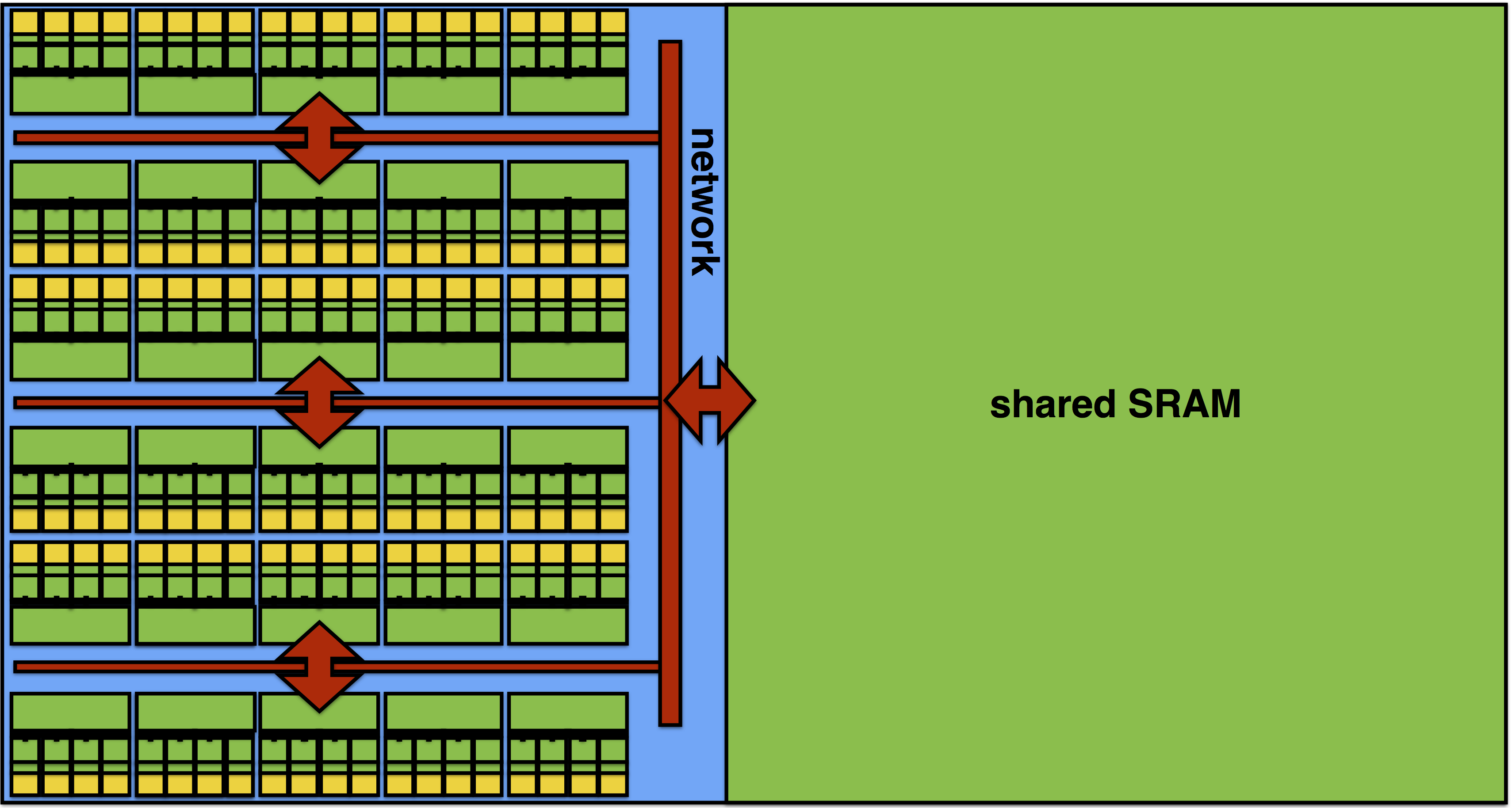

Project Crayon reconceptualizes the GPU as an array of very simple CPUs design on RISC principles. each with minimal extra features to support graphics processing. The Intel Larrabee architecture was an attempt at implementing a similar concept, but with a starting point of a Pentium pipeline, which is not competitive with simple RISC pipelines of the same era.

Why Crayon? Some of the ideas are inspired by Seymour Cray’s vector machines. I would like to call the idea a Cray on a Chip (CrayOn) but the name Cray is trademarked. As a compromise, a crayon is a graphics rendering tool of a sort – so why not Project Crayon? It does after all draw on good ideas…

To avoid confusion, the project logo is clearly a line of crayons, not a trademarked family of supercomputer companies.